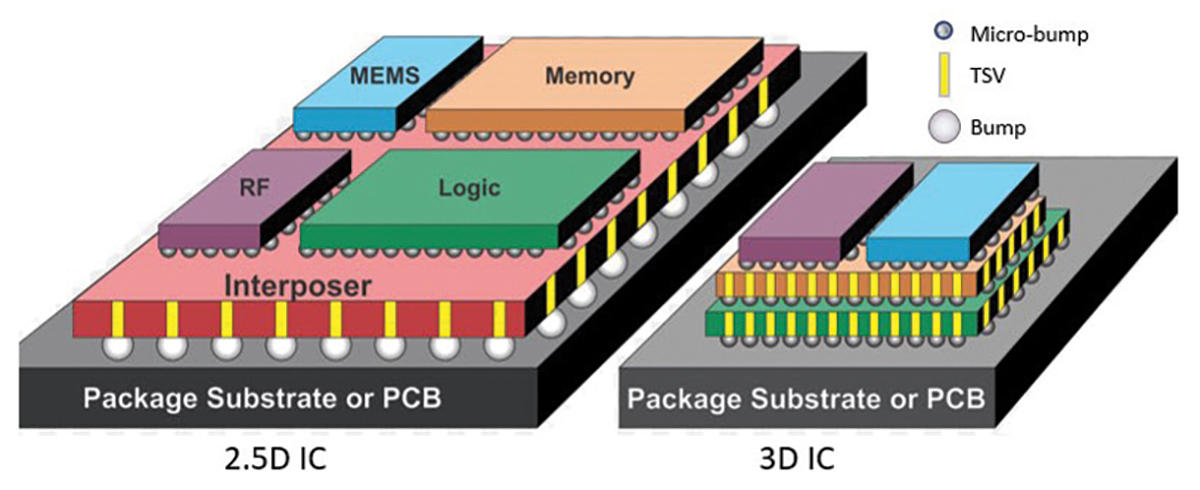

2.5D/3D IC latch-up challenges come from the advanced latch-up design rules. In 2.5D/3D active dies, two types of off-chip interfaces exist: external IOs (communicate signals externally) and die-to-die IOs (communicate between active 2.5D/3D dies). Die-to-die IOs have no connection to package pins—they drive signals via micro-bumps, the interposer, and 3D traces. Automated latch-up checking must (1) recognize external IOs for every die from the assembly level, (2) identify external diffusions (latch-up injectors) inside every die topologically (external diffusion is connected to external IO directly or indirectly through resistors, diodes, switches,…etc.), (3) assign voltages to external IOs (or latch-up injectors) from the assembly level, and propagate these voltages to every die, (4) recognize that different dies have different advanced latch‑up rules.

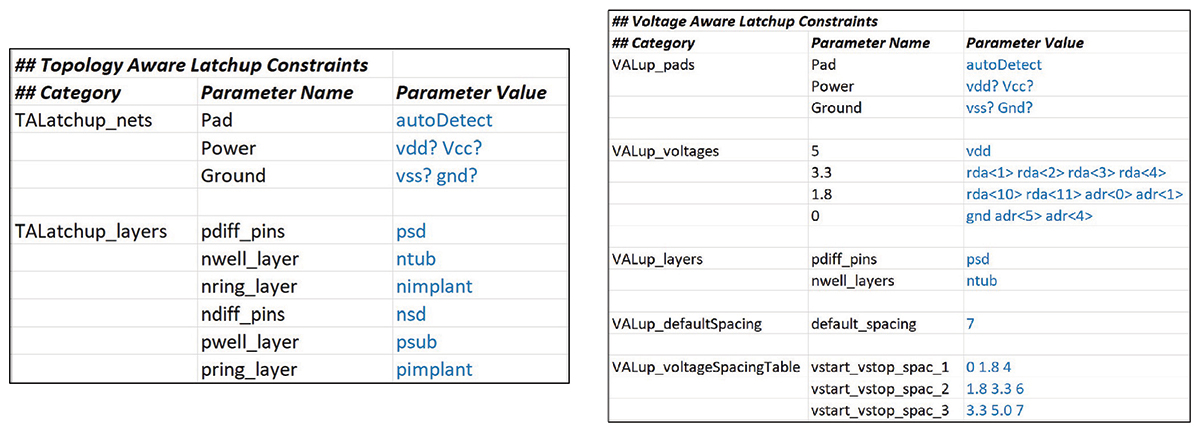

We propose two automated flows: (1) a topology-aware flow for external latch-up design rules, and (2) a voltage-aware flow for mixed voltage latch-up design rules, both starting from the assembly level, and based on automatic differentiation between external IOs and internal IOs, without using any layout markers.

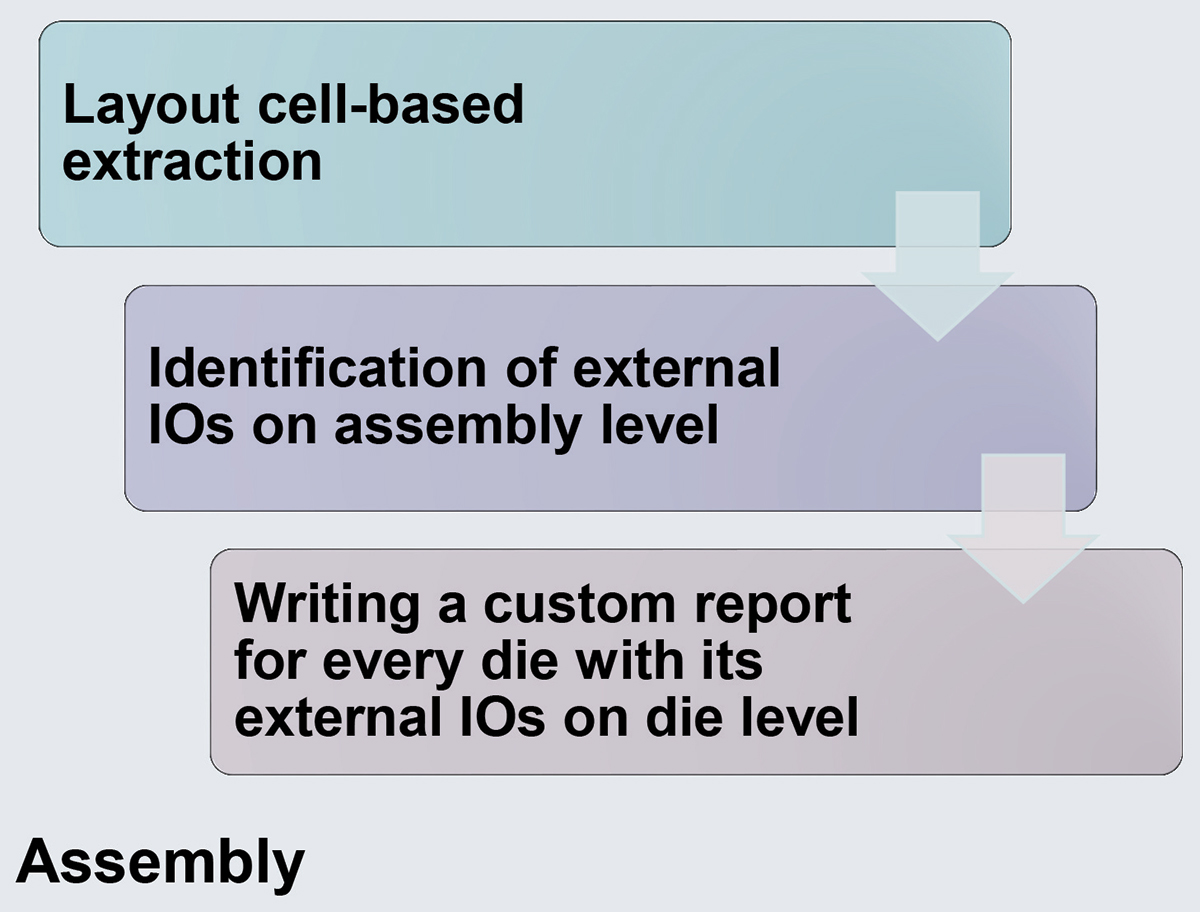

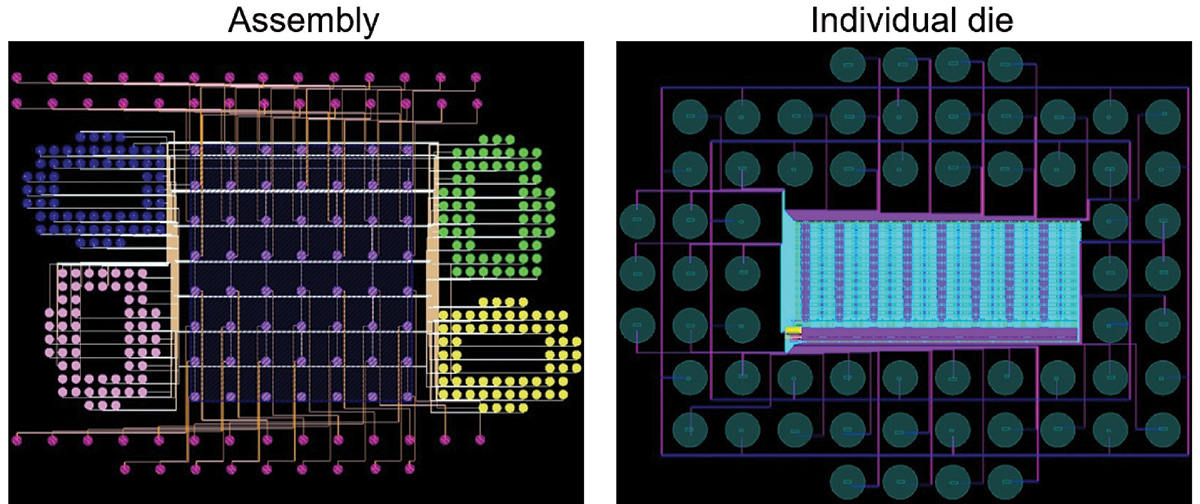

Layout cell-based extraction generates a layout netlist that describes the connections between dies, which we treat as black boxes. We identify external IOs and the port names of dies to which they connect at the assembly level, and generate a custom report for every die with its corresponding external IOs connections (Figure 2).

The topology-aware latch-up flow addresses external latch-up design rules for every die. Latch-up injectors and corresponding layout geometries are automatically identified in this flow. We can then perform external latch-up DRC measurements on relevant geometries and report violations for debugging.

The voltage-aware latch-up flow addresses mixed-voltage latch-up design rules for every die. We propagate voltages through devices from defined external ports to internal nodes in the design, enabling identification of direct/indirect connectivity of latch-up injectors. Layout geometries of the identified latch-up injectors are captured automatically. We measure the relevant geometries for mixed-voltage latch-up DRC, and report violations for debugging.

- S. Voldman, Latchup. Hoboken, NJ: Wiley, 2007.

- S. H. Voldman, C. N. Perez and A. Watson, “Guard rings: Theory, experimental quantification, and design,” EOS/ESD Symposium, 2005.

- D. Alvarez, W. Hartung, and R. Bhandari, “ESD and Latch-up failures through triple-well in a 65nm CMOS technology,” EOS/ESD Symposium, 2018.

- T. Smedes, et al., “A DRC-based check tool for ESD layout verification,” EOS/ESD Symposium, 2009.

- M. Khazhinsky, et al., “EDA approaches in identifying latch-up risks,” EOS/ESD Symposium, 2016.

- A. Oberoi, M. Khazhinsky, J. Smith and B. Moore, “Latch-up characterization and checking of a 55 nm CMOS mixed voltage design,” EOS/ESD Symposium, 2012.