Misconceptions Regarding Current Flow to the IC

here is often confusion about the interaction between IC-level component ESD protection and the appropriately required system-level ESD protection strategy. System-level ESD requirements (like IEC 61000-4-2 [1] and ISO 10605 [2]) are intended for electronic systems, not for individual integrated circuits (ICs). However, it is becoming increasingly common to see supplier claims and customer expectations of system-level ESD performance at the IC-level. While such performance may be desirous to both suppliers and customers, there is significant ambiguity about what such claims and expectations mean. Generally, little information is available about the actual system surrounding the IC. How does the customer interpret an IC-level performance claim without a specific system, and how does a supplier design for and guarantee performance? Certainly, the IC has been tested in some systems to facilitate the datasheet specification, but how did the designer define that system, and how does it compare to the final customer system? This lack of specificity implies that a general capability of the IC applies to a wide range of unique system requirements when, in fact, there are significant challenges to integrating an IC into a single unique system. These challenges extend beyond safely conducting the current during the ESD event—systems are often powered, and the failure criteria can include functional operation during and after the ESD event. But gaps exist that must be considered even if the problem is reduced to a simple guarantee that current can be safely conducted during the ESD event.

Even when only considering safe ESD current conduction, two common misconceptions must be addressed. The first is that if an IC is designed to carry the entirety of the system-level ESD current, it will be able to carry that current when placed in any system. This misconception fails to consider the impact of the full system on the current waveform and to account for modulations to the waveform that make it more severe to the IC. The second is that if an IC has higher intrinsic ESD robustness (even without carrying the full system-level ESD current), then it will be easier to protect than a competing product with lower robustness. This misconception fails to account for how current is shared between system-level and IC-level protection devices. This article will focus primarily on these two misconceptions. A future article will take a more detailed look at the gaps that arise when considering the powered-up testing and the functional failure criteria, and the steps needed to address those gaps.

On the surface, it may seem unlikely, or even impossible, that other components in the system could modulate the current waveform in such a manner that it becomes more severe to the IC. Yet, these issues do occur, creating significant challenges for both the IC designer and the system designer. Two examples of how this can happen are provided—these are by no means comprehensive of all the types of issues that can occur, but rather serve to demonstrate the complexity of the interaction between components in the system and underscore the importance of those interactions in determining the final system-level performance.

The first example is a case where a parallel capacitor is placed on the board trace of the pin being stressed. This capacitor will be charged by the ESD event, shunting some of the current away from the IC. But as this capacitor charges, its voltage increases—if the voltage exceeds the trigger voltage of the IC’s ESD cell—and that ESD cell has a clamping characteristic that is lower than the trigger voltage (i.e., a snapback device)—then the charge deposited on the capacitor can be discharged into the IC. This second discharge event has very little series impedance and can produce much higher peak currents than expected from the ESD discharge itself [3]. This type of event is highly dependent on the system. If the capacitance is small enough to limit the charge, or large enough to limit the voltage, or if the impedance between the capacitor and the IC is large enough to limit the current, then no failure will occur; if, on the other hand, the conditions are right, the IC will fail. If the IC designer has not considered this scenario and properly designed the ESD cell to account for it, significant variations in system-level results can occur, with seemingly insignificant changes to the overall system.

The above examples are by no means a comprehensive list of all the ways the current waveform could be modulated into a shape/severity not anticipated or tested by the IC designer, but rather serve to highlight the reality that such modulations do occur and that they can create nuanced failures in what are thought to be robust ESD designs.

The second misconception that must be addressed is the idea that an IC that has higher ESD robustness is guaranteed to perform better in any system-level solution. In this situation, a board-level ESD protection element is expected to conduct a majority of the system-level current, with the IC expected to share the remaining (or residual) current. In this scenario, the HBM requirement on a sub-set of the IC pins is increased, with an expectation that the IC will be able to conduct more residual current and, therefore, will outperform a competitive product with a lower rating.

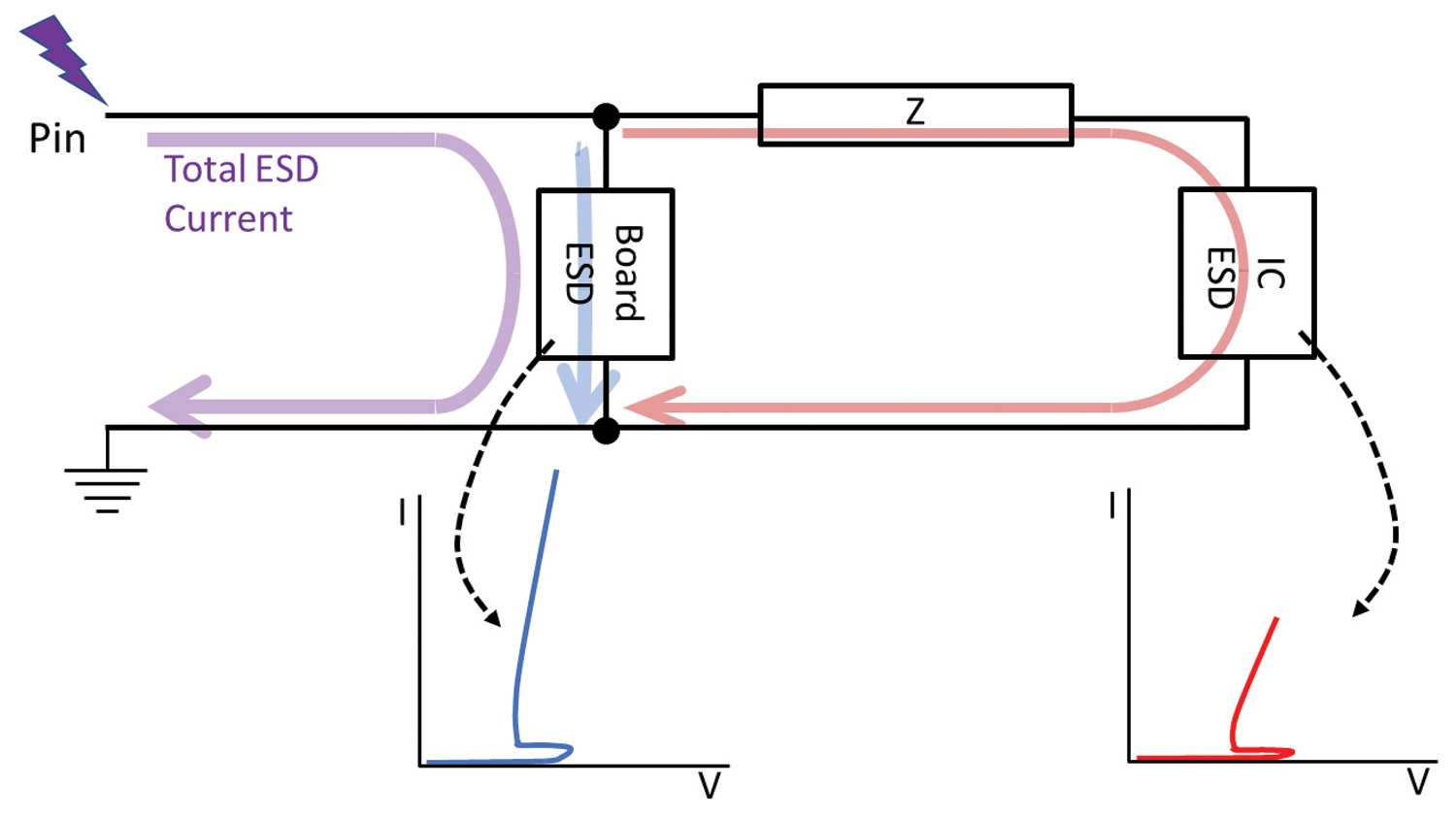

When two legs of a circuit are expected to share current in a controlled way, there are important electrical characteristics of the two legs that must be known—and the maximum amount of current that can be allowed in one of the legs is an insufficient amount of information to properly assess the circuit. Consider Figure 1; a board-level ESD Protection is placed between a Pin and Ground; a series impedance, Z, is placed in series with the IC, with its ESD protection tied to the same ground. These ESD protection elements switch from high-impedance to low-impedance at specific bias points. How current is shared between the board and the IC ESD protection will depend on many factors, which cannot be solely deduced from the ESD robustness of the IC. Consider the case where the board-level ESD Protection triggers and clamps the voltage below where the IC protection triggers; little to no current will flow into the IC, and its robustness is inconsequential. Or consider the case where the IC protection triggers and doesn’t allow the board-level protection to trigger, resulting in the IC protection conducting the entire event—its robustness is now very consequential but, as already established, insufficient to conduct the full ESD event.

Other parameters, such as the relative on-resistances of the two paths, can steer current such that the current sharing is non-optimal. The System-Efficient ESD Design (SEED) method described in [6, 7] illustrates the type of information that is required to properly design a system to share current between a board-level ESD protection element and an IC. The reader is encouraged to review this methodology for a deeper understanding of how to optimize the integration between the system and the IC. What should be clear, however, is that the robustness of the IC, without the context of the full system circuit and its parameters, is insufficient to gauge system-level ESD performance. It is quite possible to improve the robustness of the IC in a way that lowers the system-level robustness for a particular integration. The misconception that improving the IC robustness automatically leads to better system-level performance has serious consequences—increasing IC cost without guaranteeing improved performance.

This article has only dealt with misconceptions about the severity and shape of current pulses that reach the IC when integrated into a system. These misconceptions arise from a lack of recognition of how other elements in the system modulate the current waveforms delivered to the IC and how other elements in the system share current with the IC. While the ability to conduct the ESD current (whether directly or in conjunction with other elements in the system) is a critical requirement for the IC designer, it is often only the first of many requirements. If the system is powered during the ESD stress, there are added requirements for the IC designer. If that powered system is required to perform functional tasks during or after the ESD stress application, even more requirements are introduced. Future articles will explore some of these requirements in more detail and highlight some of the critical design techniques commonly used to address them.

- Electromagnetic Compatibility: Part 4-2: Testing and measurement techniques—Electrostatic discharge, IEC 61000-4-2, Edition 2, 2008

- Road vehicles — Test methods for electrical disturbances from electrostatic discharge, ISO 10605, 2008

- R. Mertens, H. Kunz, A. Salman, G. Boselli, and E. Rosenbaum, “A flexible simulation model for system-level ESD stresses with application to ESD design and troubleshooting,” Electrical Overstress/Electrostatic Discharge Symposium Proceedings, 2012, pp. 1-6.

- N. K. Kranthi, J. di Sarro, R. Sankaralingam, G. Boselli and M. Shrivastava, “Insights into the System-Level IEC ESD Failure in High Voltage DeNMOS-SCR for Automotive Applications,” 42nd Annual EOS/ESD Symposium (EOS/ESD), 2020, pp. 1-7.

- S. Bub, M. Mergens, A. Hardock, S. Holland, and A. Hilbrink, “Automotive High-Speed Interfaces: Future Challenges for System-level HV-ESD Protection and First-Time-Right Design,” 43rd Annual EOS/ESD Symposium (EOS/ESD), 2021, pp. 1-10.

- Industry Council on ESD Target Levels/White Paper 3: System-Level ESD Part I – Common Misconceptions. https://www.esdindustrycouncil.org/ic/en/documents/white-paper-3-system-level-esd-part-i-common-misconceptions

- C. Duvvury and H. Gossner, System-Level ESD Co-Design, John Wiley & Sons, 2015.