Two-Pin HBM Testing: a New Option?

uman Body Model (HBM) is the original ESD test method for semiconductor devices and is still the most widely used ESD test [1]. This article will discuss the old, but now new two-pin HBM tester. Not only are the new two-pin testers not subject to one of the drawbacks of today’s high pin count testers, they provide additional testing convenience and diagnostic options not available in traditional HBM testers.

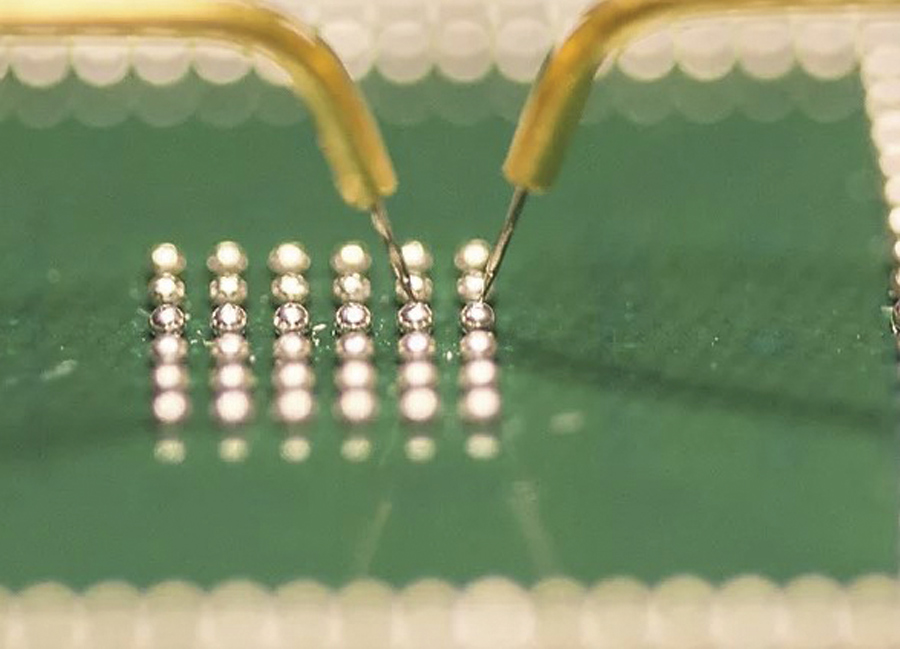

The use of wafer probes for pulse delivery has obvious advantages. HBM testing can be done conveniently at both wafer and package level. At the package level, there is no need for a socket, eliminating the cost, design effort, and time delays that are often associated with HBM testing.

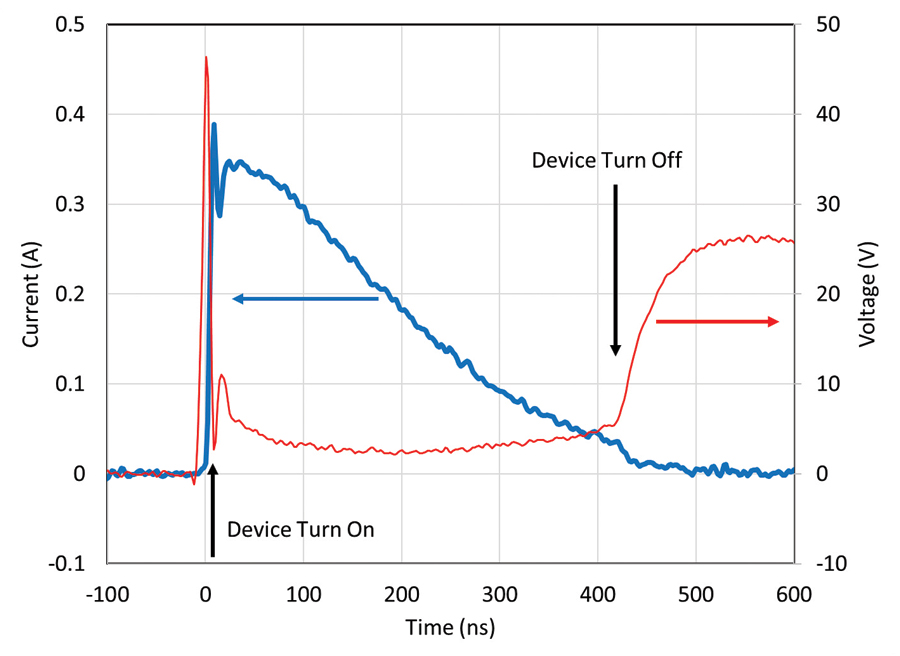

Measuring voltage across a DUT during the pulse also makes it possible to capture the exact time of failure. Device failure is often accompanied by an abrupt drop in voltage across the DUT.

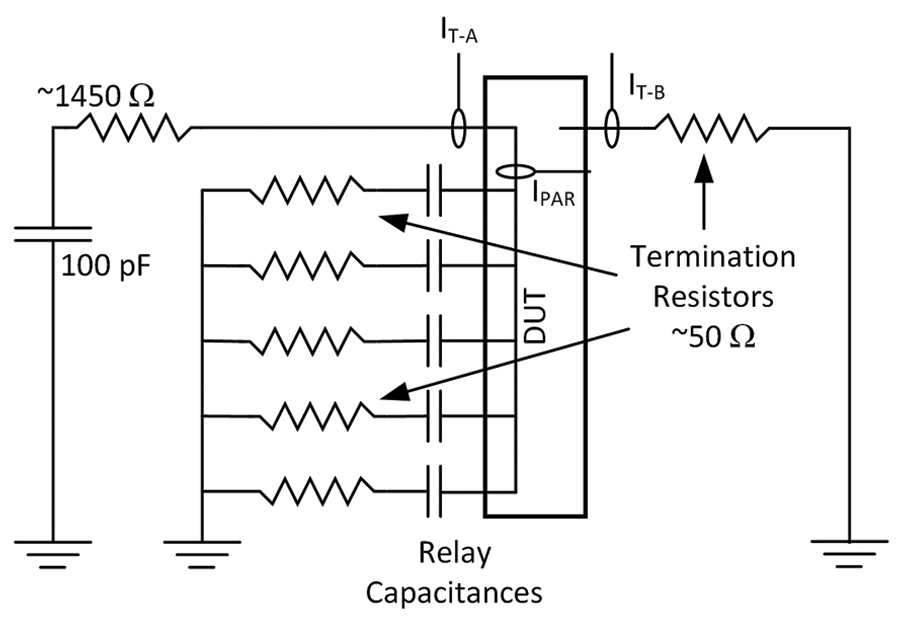

There has been occasional criticism of the GTS Pure Pulse system that it is not a true 1500-ohm source impedance but is a 50-ohm source delivering an HBM current waveform. This is not valid. The waveform is formed using an RCL network similar to those used in a matrix-based tester, which is then delivered over a short 50-ohm line. The situation is actually the same in a matrix-based tester. The pulse is formed with an RLC circuit but is then delivered to the DUT over a series of traces and connections which all have characteristic impedances that are certainly not 1500 ohms but are not as well controlled as using RF probes.

The single area where two-pin testers create a challenge for the test engineer is the implementation of the pin combinations in JS-001 for a two-pin tester. That could be the topic of a future article.

- ANSI/ESDA/JEDEC JS-001-2017, “For Electrostatic Discharge Sensitivity Testing Human Body Model (HBM) – Component Level.”

- Duvvury, et al., “Gate Oxide Failures Due to Anomalous Stress from HBM ESD Testers,” EOS/ESD Symposium, 2004, pp. 132 – 140.

- Ashton, et al., “Voltages Before and After HBM Stress and Their Effect on Dynamically Triggered Power Supply Clamps,” EOS/ESD Symposium 2004, pp. 153 – 159.

- R. Ashton, “HBM Pin Combinations,” In Compliance Magazine, December 2019.

- H. Kunz, R. Steinhoff, C. Duvvury, G. Boselli, and L Ting, “The effect of high pin-count ESD tester parasitics on transiently triggered ESD clamps,” 2004 Electrical Overstress/Electrostatic Discharge Symposium.

- M. Chaine et al. , “HBM tester parasitic effects on high pin count devices with multiple power and ground pins,” 2006 Electrical Overstress/Electrostatic Discharge Symposium.

- Grund Technical Solutions (GTS), Pure Pulse, https://www.grundtech.com/purepulse.

- High Power Pulse Instruments (HPPI), Two-Pin HBM Tester, https://www.hppi.de/files/HBM-S1-B.pdf and https://www.hppi.de/files/HBM-TS10-A.pdf.

- R. Ashton, S. Fairbanks, A. Bergen, and E. Grund, “Electrostatic test structures for transmission line pulse and human body model testing at wafer level,” 2018 IEEE International Conference on Microelectronic Test Structures (ICMTS).