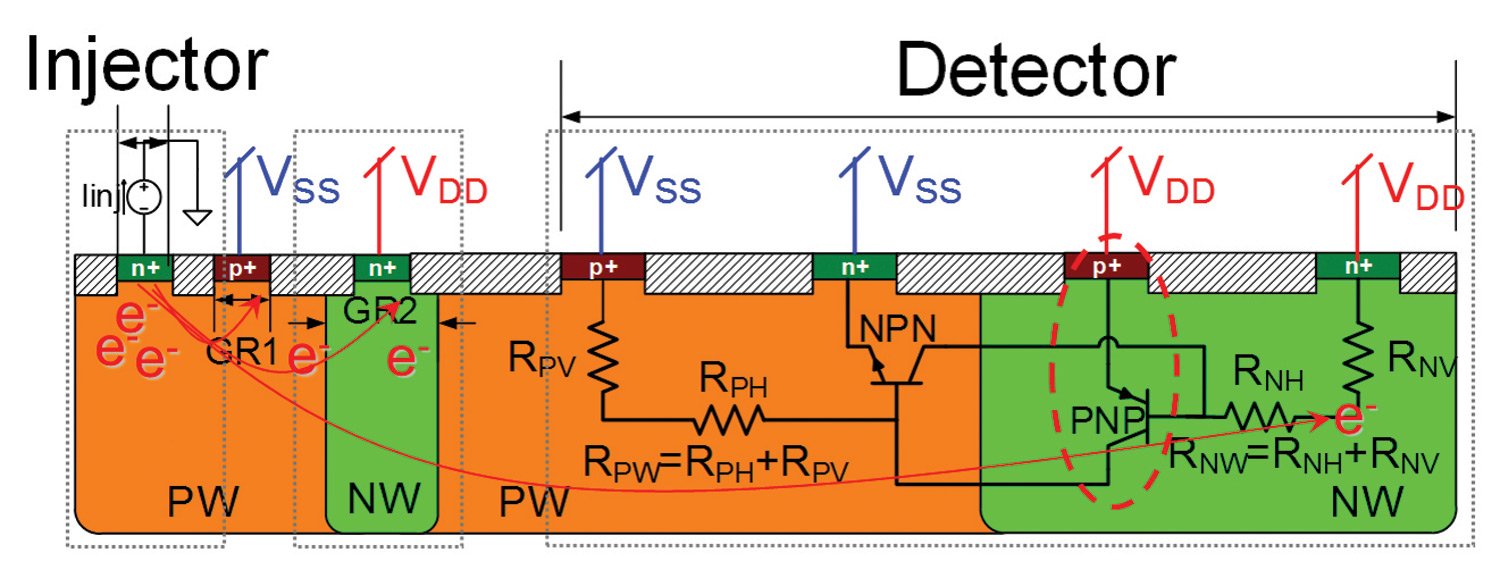

To reduce the ELU risk, designers also have a few other options. Designers can either increase the distance between the injector and the victim device or increase the width of the guard ring which surrounds the injecting I/O cell. The wider the guard ring is, the more carriers will be contained within the I/O cell. Designers can also add a guard ring around the core circuit to reduce the amount of carrier reaching out to the victim device or reduce the well tape spacing in the core circuit to create a harder latch-up triggering condition. The overall design strategy to eliminate the ELU risk is a trade-off scenario for designers, and the solution should be customized based on the chip scheme.

Overall, latch-up prevention is one of the most important tasks for both foundries and IC designers. Based on the chip design scheme, designers should select proper solutions to eliminate the ILU and ELU risks in chip design, referencing the foundry guidelines and latch-up silicon data to ensure minimal latch-up risks for the product.

- W. Liang, R. Gauthier, S. Mitra and H. Lai, “External latch-up Risks and Prevention Solutions in Advanced Bulk FinFET Technology,” 2019 41st Annual EOS/ESD Symposium (EOS/ESD), 2019, pp. 1-9, doi: 10.23919/EOS/ESD.2019.8869999.