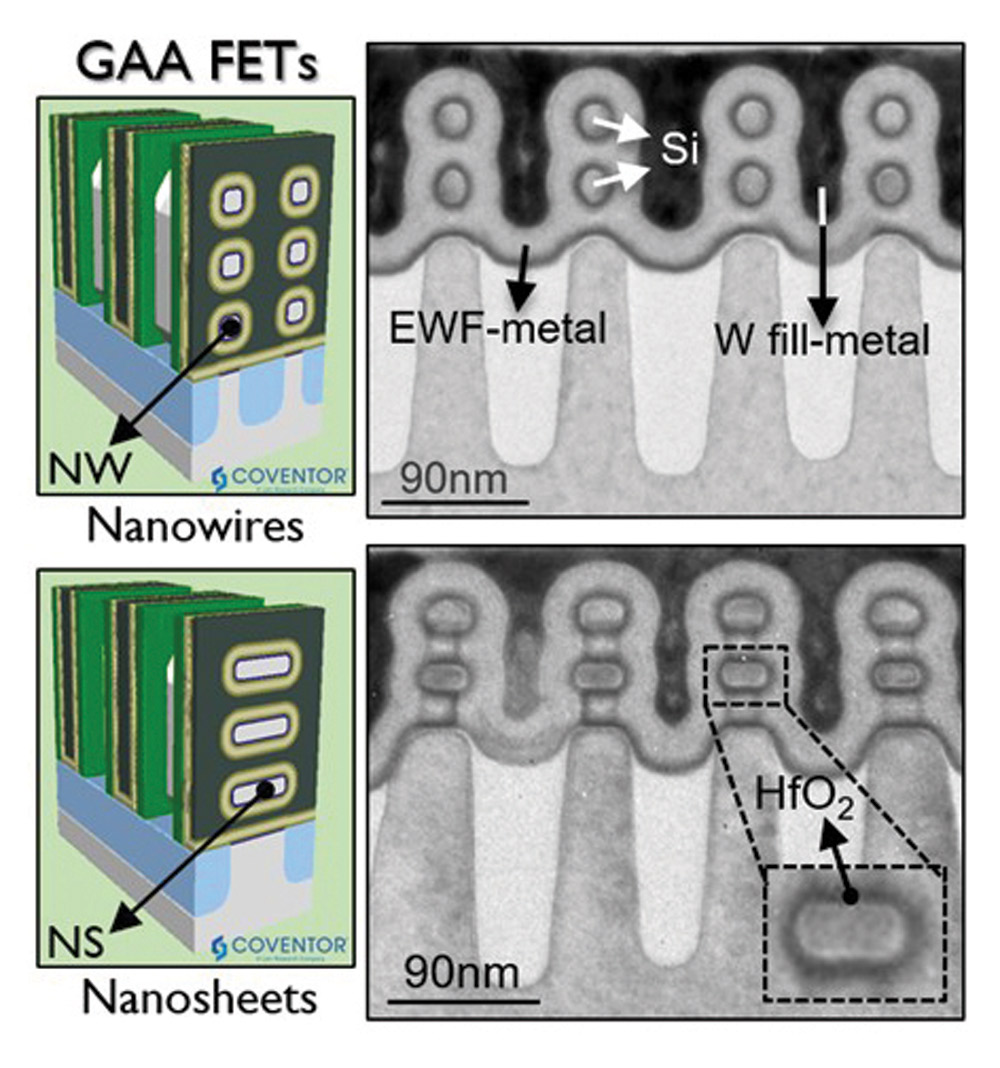

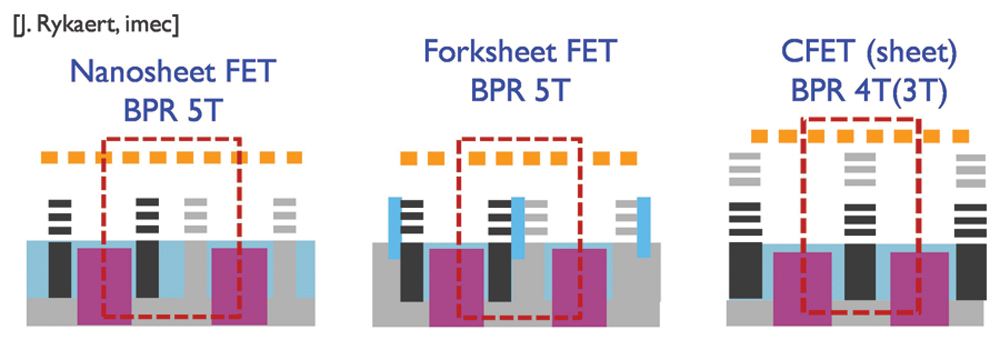

oughly a decade ago, starting at 22nm technology nodes, the transistor architecture changed from planar to FinFET [1-3]. Bulk FinFET (FF) which is a multi-gate transistor built on Si substrate has been the mainstream in the state-of-the-art logic CMOS technologies for many mobile SoC applications [1-3]. Fortunately, ESD reliability has not been an obstacle in the FinFET era from 22nm to 5nm technology nodes. Nowadays, with the increased requirements of high-performance computing applications, logic CMOS technologies need further evolutions. Several new transistor architectures have been proposed to achieve more powerful computing capability. In this article, we will look at the impacts of these transistor architectures on ESD reliability.

In addition to the new GAA transistor architecture, the integration of a Source/Drain (S/D) dual epitaxy process with strain engineering [3, 12-15] has been proposed to continuously enable better, faster, and more compact devices [13]. For example, in p-type MOSFETs, the Si S/D epitaxy structure is replaced by a SiGe S/D epitaxy structure [13-15] for providing the channel strain engineering. These examples of architecture and material options can bring critical challenges of ESD reliability.

One measure of ESD performance in these new device structures is to characterize diodes as a way of assessing their impact. Prior research has shown the investigations of ESD diodes in SOI and bulk FinFET technologies [16, 17]. ESD diodes in bulk Si GAA vertically-stacked horizontal nanowires (NW) technology have been also reported [18]. In addition, the impact of the material options with SiGe S/D epitaxy on the bulk FF ESD diode performance has also been shown [15, 19]. In this article, the influence of the SiGe epitaxy stressor on bulk GAA NS ESD diodes will be disclosed.

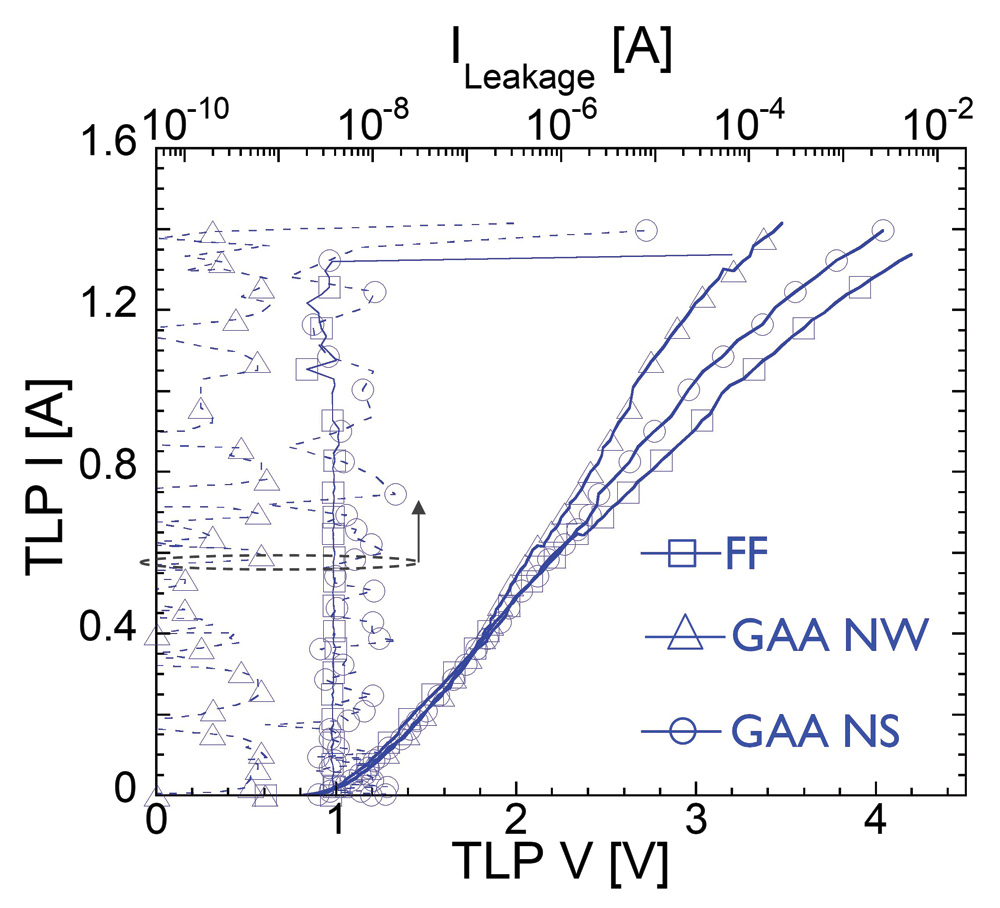

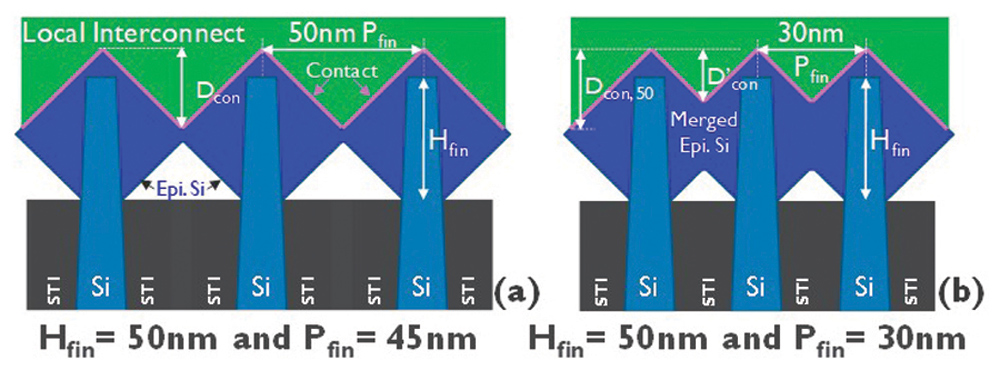

One outcome in the architecture change from FF to GAA NW, due to a different fin height (Hfin) in these two technologies, is that the ESD diodes have different thermal behaviors. A taller fin structure usually has a large epitaxial volume on the anode and cathode regions [18]. This improves the thermal dissipation and results in less self-heating and lower Ron under 100ns TLP stress. However, this taller fin architecture with a reduced fin pitch can result in a smaller contact area at the S/D regions due to the S/D epitaxy growth and the middle-of-line (MOL) process modules, which can impact ESD diode failure levels, as illustrated in Figure 3. With a Hfin of 50nm and a fin pitch (Pfin) of 45nm, the S/D epitaxy growth between any two fins results in their adjacent epitaxy regions merging. This allows an increased area of the contact scheme in MOL local interconnect (LI) processes, as shown in Figure 3a. The contact scheme depth (Dcon) is defined by the top of a Silicon (Si) epitaxy structure and the bottom of a LI recess ending depth in ILD0 layer. With a reduced Pfin of 30nm, the Si epitaxy structure between two fins will be merged, resulting in a reduced contact depth (D’con), as shown in Figure 3b. Taller fins with a further reduced Pfin will have more merged epitaxy volume. The contact scheme along the fin length has been shown to impact It2 [17]. The reduced Dcon can be expected to bring a negative impact on ESD diode performance, increasing its thermal heating under ESD and hence lower failure current. Fortunately, the original fin pitch in sub-5nm GAA NS technology can be relaxed from the industrial 7nm/5nm FF technologies [10]. Therefore, the impact of S/D material options on ESD diode performance can be more critical in GAA NS technologies.

- S. Natarajan, et al., “A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size,” IEDM Tech. Dig., 2014, p. 3.7.1-3.7.3.

- C. Auth, et al., “A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts, and high-density MIM capacitors,” VLSI Tech. Dig., 2012, p. 131-132.

- E. Rosseel, et al., “Characterization of Epitaxial Si:C:P and Si:P Layers for Source/Drain Formation in Advanced Bulk FinFETs,” ECS Transactions, vol. 64, no. 6, p. 977-987, 2014.

- K. J. Kuhn, “Considerations for Ultimate CMOS Scaling,” IEEE Trans. on Electron Devices, vol. 59, no. 7, p. 1813, 2012.

- S.-G. Hur, et al., “A practical Si nanowire technology with nanowire-on-insulator structure for beyond 10nm logic technologies,” IEDM Tech. Dig., 2013, p. 646.

- I. Lauer, et al., “Si nanowire CMOS fabricated with minimal deviation from RMG FinFET technology showing record performance,” VLSI Tech. Dig., 2015, p. 142.

- H. Mertens, et al., “Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates,” VLSI Tech. Dig., 2016, p. 142.

- C. Dupre, et al., “15nm-diameter 3D stacked nanowires with independent gates operation: ΦFET”, in IEDM Tech. Dig., 2008, p. 749.

- H. Mertens, et al., “Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates,” IEDM Tech. Dig., 2016, p. 158.

- N. Loubet, et al., “Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET,” VLSI Tech. Dig., 2017, p. T-230-231.

- R. Ritzenthaler, et al., “Vertically Stacked Gate-All-Around Si Nanowire CMOS Transistors with Reduced Vertical Nanowires Separation, New Work Function Metal Gate Solutions, and DC/AC

Performance Optimization,” IEDM Tech. Dig. 2018, p. 508. - A. Hikavyy, et al., “Properties and growth peculiarities of Si0.30Ge0.70 stressor integrated in 14 nm fin-based p-type metal-oxide-semiconductor field-effect transistors,” Thin Solid Films, vo. 602, Mach 2016, p. 72–77.

- T. Chiarella, et al., “Towards high performance sub-10nm finW bulk FinFET technology,” Proc. of ESSDERC, 2016, p. 131-134.

- E. Bury, B et al., “Self-heating in FinFET and GAA-NW using Si, Ge and III/V channels,” IEDM Tech. Dig., 2016, p. 15.6.1-15.6.4.

- S.-H. Chen, G et al., “Towards optimal ESD diodes in next-generation bulk FinFET and GAA NW technology nodes,” IEDM Tech. Dig., 2017, p. 7.4.1.

- A. Griffoni, et al., “Next-generation bulk FinFET devices and their benefits for ESD robustness,” Proc. of EOS/ESD Symp., 2009, p. 76.

- S.-H. Chen, et al., “Gated and STI defined ESD diodes in advanced bulk FinFET technologies,” IEDM Tech. Dig., 2014, p. 514.

- S.-H. Chen, et al., “ESD diodes in a bulk Si gate-all-around vertically stacked horizontal nanowire technology,” IEDM Tech. Dig., 2016, p. 35.4.1.

- S.-H. Chen, et al., “Transient Overshoot of Sub‑10nm Bulk FinFET ESD Diodes with S/D Epitaxy Stressor,” Proc. of EOS/ESD Symp., 2019, p. 1-6.

- S.-H. Chen, et al., “ESD Protection Diodes in Sub‑5nm Gate-All-Around Nanosheet Technologies,” Proc. of EOS/ESD Symp., 2020, p. 1A.2.1-8.

- J. Ryckaert, et al., “Enabling Sub-5nm CMOS Technology Scaling Thinner and Taller!” IEDM Tech. Dig., 2019, p. 685.

- P. Weckx, et al., “Novel forksheet device architecture as ultimate logic scaling device towards 2nm,” IEDM Tech. Dig., 2019, p. 871.