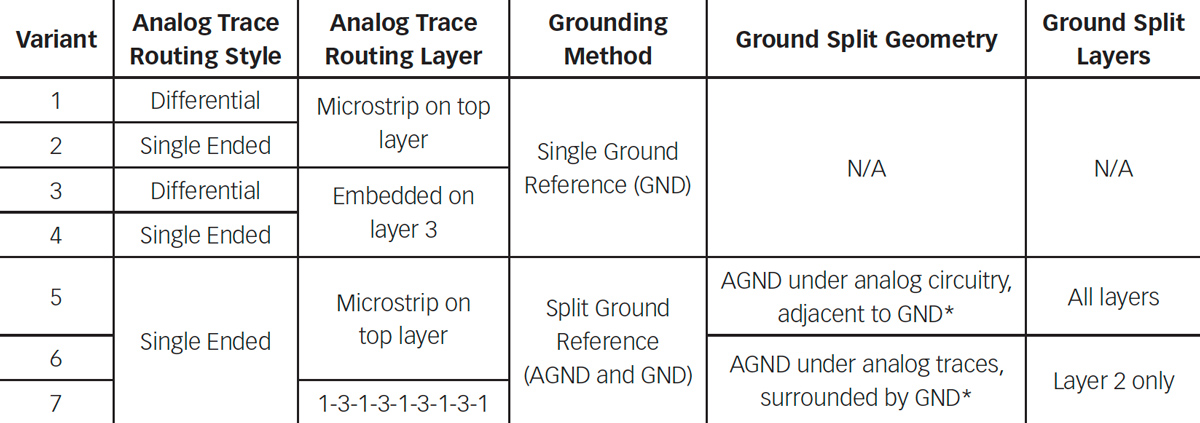

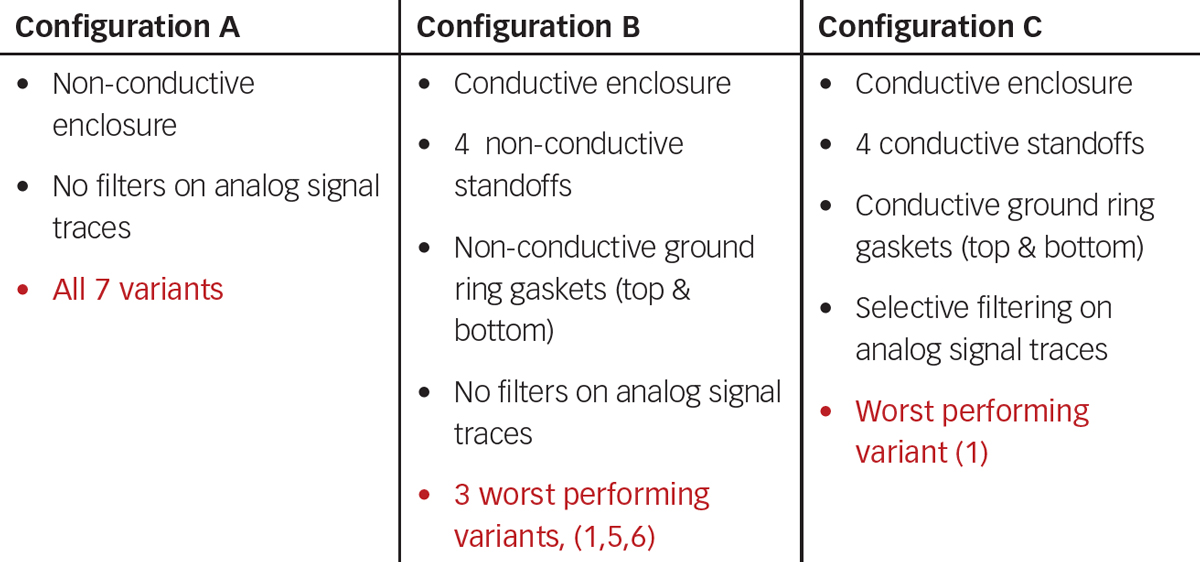

his month’s column is the last of three parts devoted to designing, testing, and EMC immunity evaluation of multilayer PCBs containing analog circuitry. The first article presented a top-level block diagram description of the design problem under research [1,2]. The second article discussed the radiated immunity results [3]. This article is devoted to the conducted immunity testing according to the ISO11452-4 Bulk Current Injection from 1 MHz – 400 MHz up to severity level 4. As a reminder, two analog measurements are present on the PCB. The first analog measurement captures analog temperature values from an NTC thermocouple at the end of a short harness. The second analog measurement captures the analog voltage of 12 volts connected at the banana jack terminals of the PCB. Both sets of values are processed by the microcontroller and reported to the test engineer outside the chamber via UART and fiber optic communications for isolation. However, for the purposes of this article, only analog temperature measurements are presented and discussed.

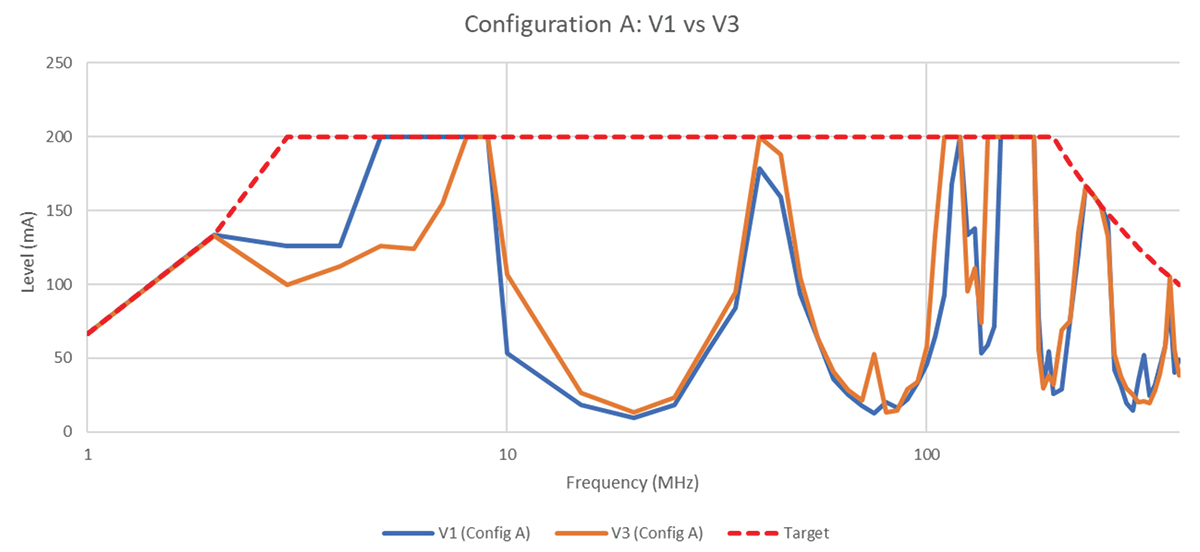

Next, Variant 3 was tested and the results were compared to those of Variant 1. The comparison is shown in Figure 3 on page 44.

Observations: Variant 1 performed better than Variant 3 at lower frequencies (2 to 7 MHz) and slightly better at higher frequencies. Beyond 10 MHz there aren’t significant differences between the two variants. This demonstrates that burying differentially routed traces beneath the ground plane on layer 2 did not provide an overall benefit above 7 MHz.

Next, Variant 4 was tested and the results were compared to those of Variant 2. The comparison is shown in Figure 4.

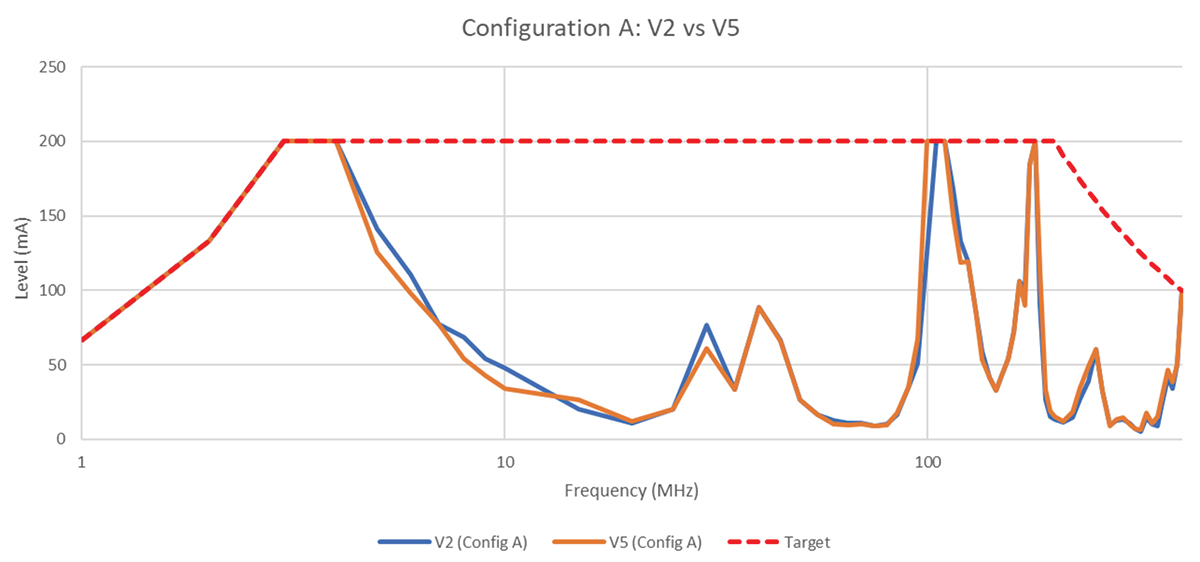

Next, Variant 5 was tested, and the results were compared to those of Variant 2. The comparison is shown in Figure 5.

Observations: Variant 5 performed similarly to Variant 2 across the entire spectrum. This demonstrates that splitting the grounds (GND and AGND) has a negligible impact on the conducted immunity performance. This is likely due to the fact that while there is a split between the two references, they both allow for a continuous reference return adjacent to the analog trace routes to provide a low inductance RF return path.

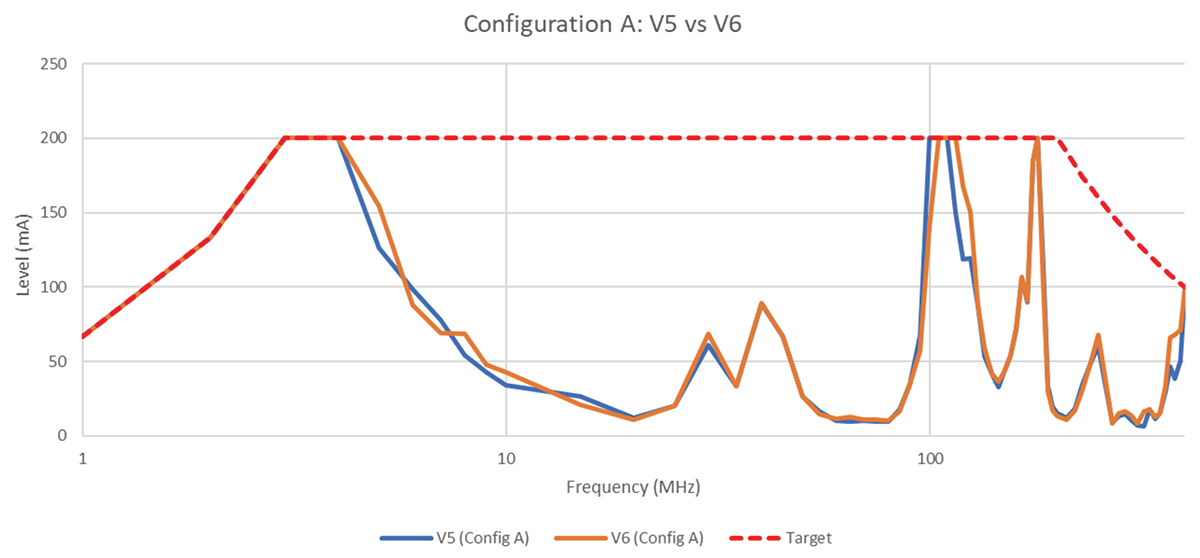

Next, Variant 6 was tested and the results were compared to those of Variant 5. The comparison is shown in Figure 6.

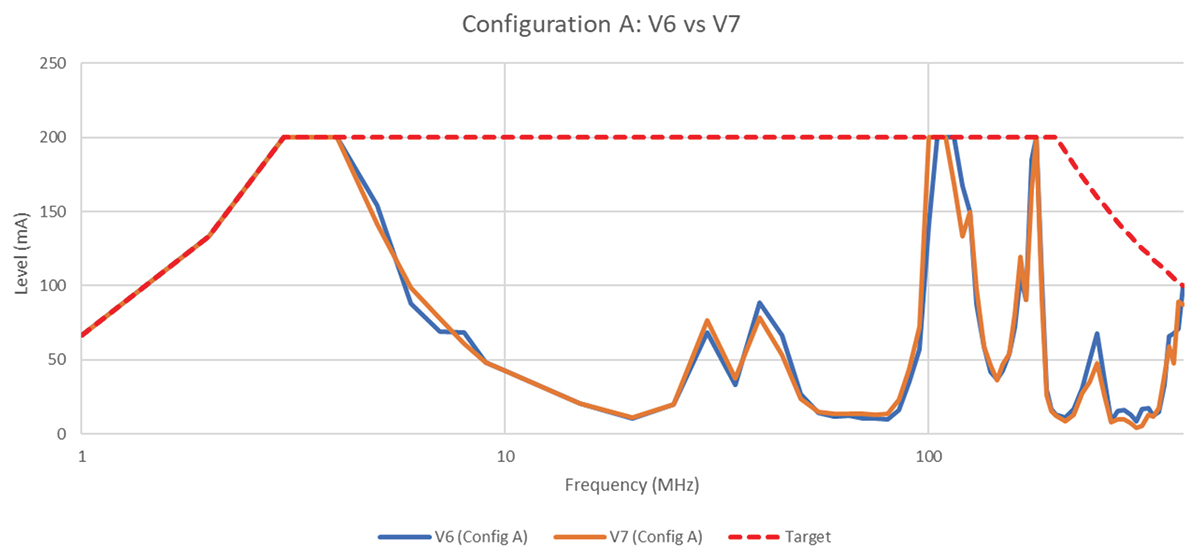

Next, Variant 7 was tested and the results were compared to those of Variant 6. The comparison is shown in Figure 7.

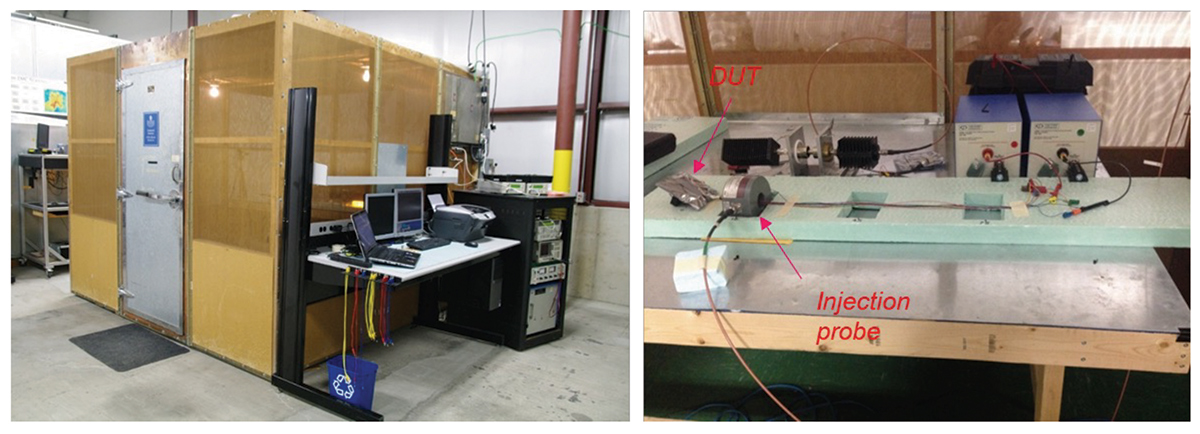

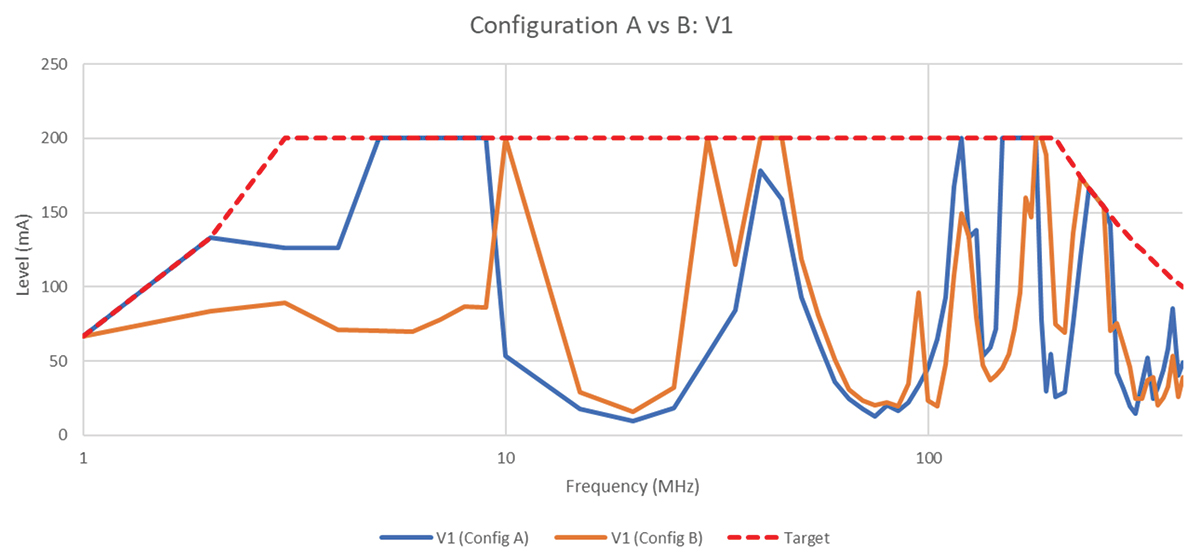

Figure 8 compares the test results for Variant 1, Configuration A vs. B.

Observations: Variant 1 in Configuration A generally outperforms Configuration B up to 9 MHz and beyond 90 MHz. Between 9 MHz and 90 MHz, Configuration B shows a benefit. Based on the data, an ungrounded shielded enclosure provides benefit in a limited frequency range when routing the analog trace differentially on the top side.

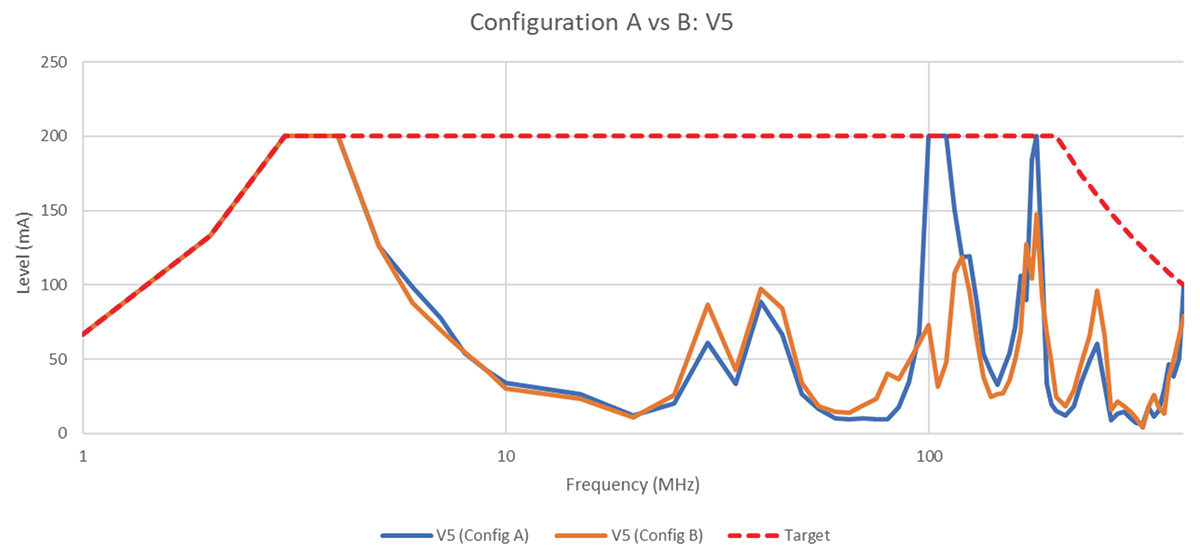

Figure 9 compares the test results for Variant 5, Configuration A vs. B.

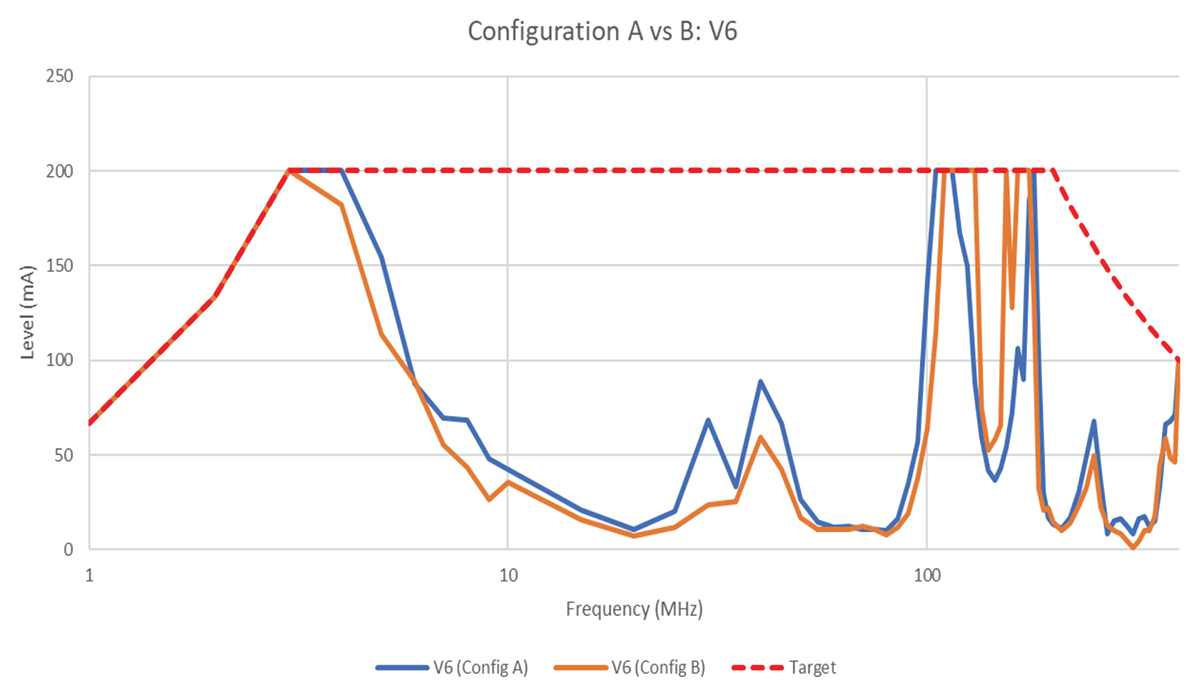

Figure 10 compares the test results for Variant 6, Configuration A vs. B.

Observations: Variant 6 in Configuration A performed better than Configuration B with the exception of the frequency range 110 MHz – 180 MHz where the ungrounded shielding provides some benefit. However, there are inconsistent benefits overall of introducing an ungrounded conductive enclosure (Configuration B). In Variant 6, the analog traces are routed on the top layer with PCB GND surround and a separate Analog GND is beneath on Layer 2. All other layers are PCB GND. These layout design features minimize the ungrounded shielded enclosure’s impact on the conducted immunity performance.

- Baatar, B., Costantino, C., Morey, R., Muldowney, C., EMC PCB Design Study, GVSU senior project sponsored by E3 Compliance, LLC.

- Adamczyk, B., Mee, S., Baatar, B., “Evaluation of PCB Design Options using a Multilayer PCB – Part 1: Top-Level Description of the Design Problem,” In Compliance Magazine, May 2022.

- Adamczyk, B., Mee, S., Baatar, B., “Evaluation of PCB Design Options using a Multilayer PCB – Part 2: Radiated Immunity Results,” In Compliance Magazine, June 2022.

- Adamczyk, B., Mee, S., “Bulk Current Injection (BCI) – Substitution Method and Closed-Loop Method with Power Limitation,” In Compliance Magazine, June 2018.