his article introduces typical latch-up verification techniques to detect and prevent latch-up. These techniques rely on electronic design automation (EDA) tools to deliver the coverage necessary to identify and eliminate latch-up risks.

While there is a common understanding of the physical phenomena leading to latch-up across the industry, verification methods to identify these risks vary. The Latch-up EDA Technical Report [3] outlines several EDA verification flows and tools used throughout the industry to uncover latch-up risks. The report provides an overview of scenarios beyond conventional latch-up, including grounded and biased n-wells, transient latch-up, native devices, radiation-induced latch-up, and special high voltage (HV) and FinFET technology requirements. The technical report includes a description of power management and system-level latch-up challenges and consideration of triggering parasitic structures during unpowered ESD events. The report provides a reference for latch-up prevention design rules classified based on physical category and EDA implementations.

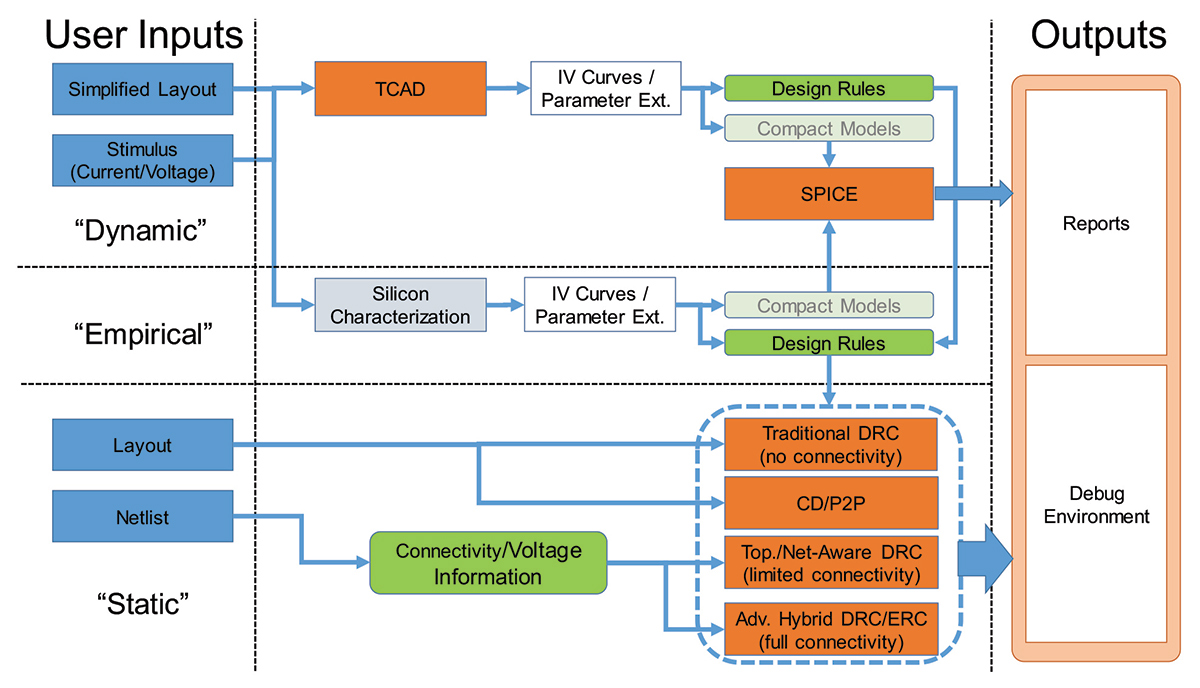

- Dynamic

- Empirical

- Static

Dynamic analysis leverages EDA tools that simulate device and semiconductor material (including substrate) behavior, which may also include the underlying physical phenomena. The compute-intensive nature of these techniques limits scalability, relegating simulation-based techniques to specific areas of a design and/or simplified layouts. Dynamic analysis is often used to characterize and perform analysis in identifying latch-up conditions that may form the basis of design rules used in (predominantly static) EDA tools. EDA tools, such as those based on field solver technology, technology CAD (TCAD), and SPICE simulation, fall within this category.

Empirical analysis techniques use (portions of) actual silicon die to characterize the limits of latch-up robustness. Specific areas of these dice often contain test structures used to perform such characterization for a particular process node and metal stack. Automation of these tests may be done to ensure consistency and repeatability. Once characterized, these findings are used to develop design rules used in (predominantly static) EDA tools. As empirical methods are more closely aligned with physical device characterization.

Static verification flows generally check design rules (constraints) derived from dynamic and empirical measurements to evaluate the robustness of the design. This evaluation often focuses on the physical implementation (layout) and may utilize several techniques to provide a holistic view of latch-up susceptibility. These techniques generally include design rule checks (DRC), often without connectivity considerations, current density (CD) and point-to-point (P2P) resistance, along with hybrid approaches that leverage connectivity and voltage information to perform topology/net aware DRC checking with limited connectivity, as well as advanced hybrid DRC and electrical rule check (ERC) with full connectivity. These hybrid verification approaches are often described as being “context-aware” due to considerations of topology and voltage. The context (the type of net or voltage considerations) influences the outcome of an otherwise static rule that may be overly conservative had the design context not been made available.

For this reason, context-aware verification techniques are desirable for their ability to mitigate the application of over-constrained design rules. Static approaches scale to full-chip levels of the design and can be used for design sign-off. Static approaches identify “at-risk” areas while providing a cohesive debugging environment from schematic and other EDA views.

A graphical representation of these verification flows is shown in Figure 1 on page 50.

Latch-up verification is a complex task requiring detailed knowledge of the impacts and interactions of the manufacturing process, design style, and mitigation techniques. EDA tools can significantly improve the quality of this verification, particularly when the context of electrical connectivity and consideration of the voltages applied to the design are also leveraged.

Finally, latch-up EDA tools are mature and sophisticated so they help guide the designers to prevent potential latch-up failures before the IC design tape out. However, it is good to note that the EDA checks are developed based on the best available information and sometimes written conservatively. Therefore, there is always room for interpretation and flexibility in special cases where designs may constrict.

With such diversity, the specific implementation of latch-up verification flows is expected to differ from company to company, with each foundry having its own best practices. Simultaneously, unique device variations, design margins, and design methodologies contribute to specific differences in effective implementation and verification strategies selected for latch-up prevention in different process nodes. However, the fundamental verification concepts described within this technical report should still hold true. As more latch-up EDA solutions become commercially available, along with increased foundry adoption, further opportunities for standardizing latch-up EDA verification approaches and specific latch-up checks will become available.

- R. Troutman, Latchup in CMOS Technology: The Problem and Its Cure, Kluwer Academic Publishers, NY, 1986.

- IC Latch-up Test, JEDEC Standard JESD78F, January 2022. Available: https://www.jedec.org/system/files/docs/JESD78F.pdf

- M. Khazhinsky, et al, “Technical Report for Latch-up Electronic Design Automation,” ESDA Technical Report ESD TR18.0-02-20, 2021. Available: https://www.esda.org/store/standards/product/307/esd-tr18-0-02-20