To answer the question of what causes EOS failures, a holistic approach needs to be taken. While absolute maximum ratings (AMR) are published in product datasheets, they don’t address the limitations due to the inherent transients that the components experience due to several reasons such as inductive coupling, EMI/EMC, etc. that are typically application specific. The presence of these transients which range from Direct Current (DC) to nanosecond (ns) and their impact on component reliability are often not considered mainly because of the lack of understanding of their effects.

The curves with less transient times do not necessarily shift in a parallel fashion as shown by the blue and green solid curves. One can envision that since the power to failure from the well-known Wunsch-Bell relation is a function of time to failure, the true shifts in these probability curves might involve a stochastic process. We can perhaps try to represent them with the dashed blue and green curves to convey that at lower stress levels the shift for transient pulses would be less compared to the shift at higher stress levels. These cannot be confirmed without detailed studies that include field relevant studies and gathering data that relate to various transient conditions and their impact on robust system designs. There are complex parameters involved such as minimum stress to create thermal damage, power to failure versus pulse widths for specific example case studies, and an understanding of statistical reliability models and the limits and regions of their applications, etc.

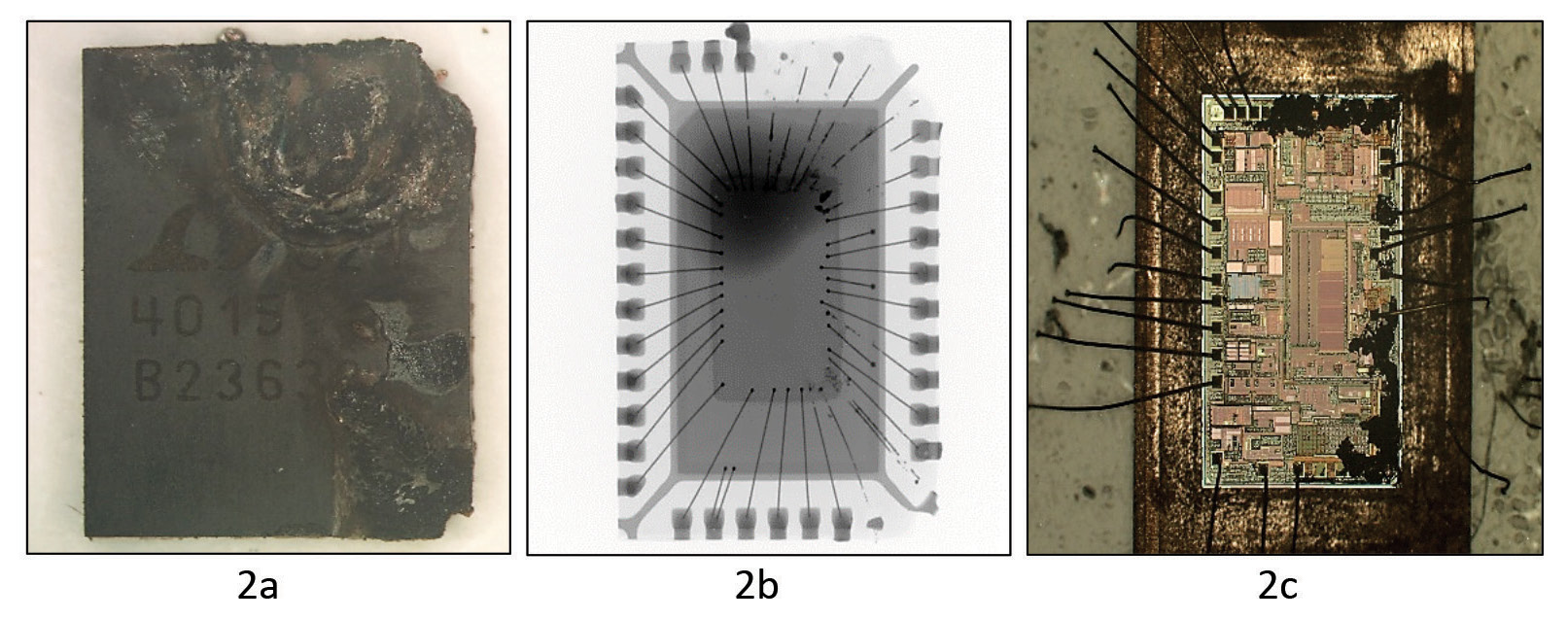

There have been several case studies from different applications published in Industry Council WP4 [1]. The common thread among the cases appears to be a lack of clarity on the specifications for absolute maximum rating for transient signals. It becomes even more important in high-reliability applications such as automotive, medical, and aerospace.

As a final note, there is much to be investigated on this complicated subject of tAMR. The Industry Council on ESD Target Levels plans to publish a new extension of White Paper 4 on the subject soon.

- Industry Council White Paper 4, JEP174. https://www.jedec.org/document_search?search_api_views_fulltext=jep174