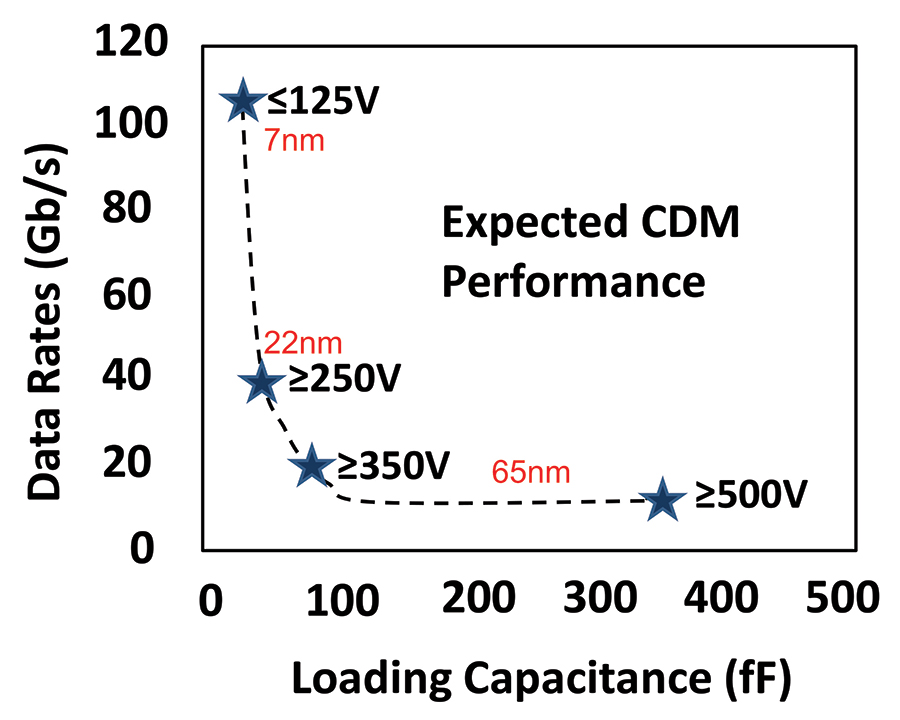

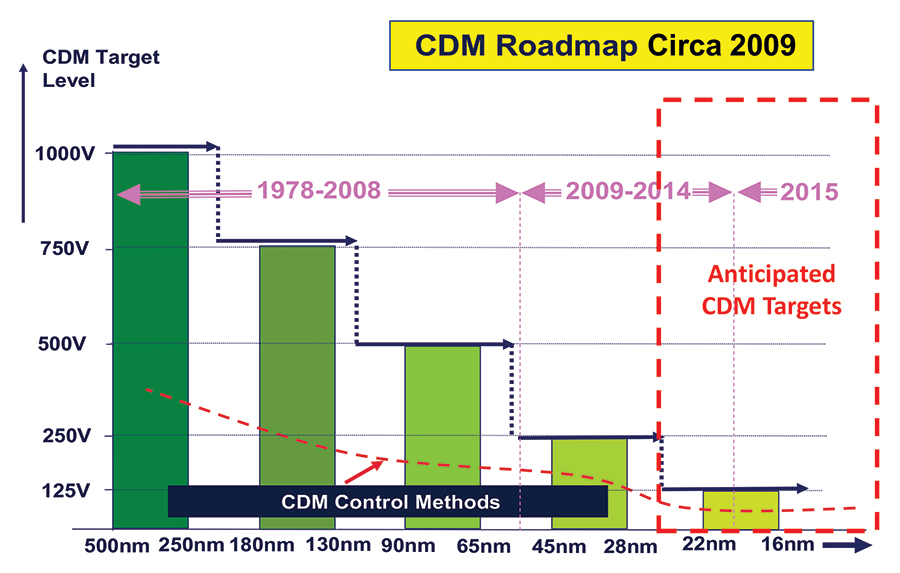

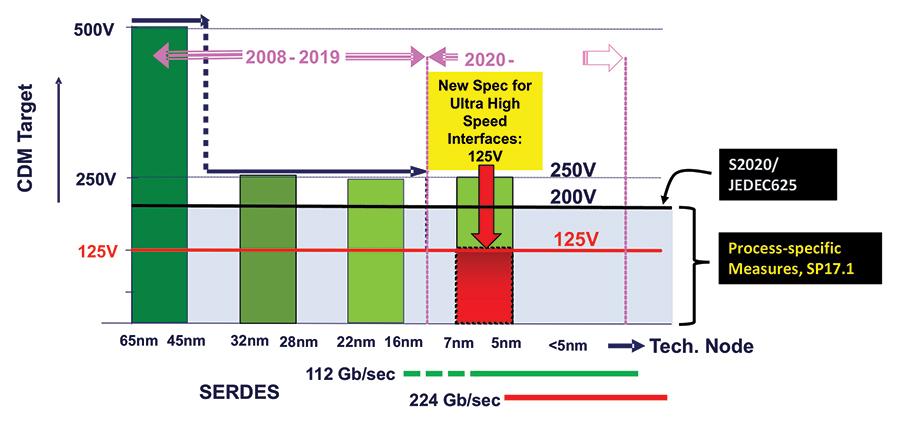

It was in 1974 that Thomas Speakman that first mentioned, “CDM is as important as HBM” [1]. Also, credit should be given to Bossard et al. for first reporting about triboelectrically charged pins [2]. Then during the mid-1980s, workers from British Telecom performed the first experiments on the field-induced CDM threat [3]. This was quickly followed by the work of Siemens, where they demonstrated evidence of DRAM devices failing due to uncontrolled CDM in a production area. These events motivated the serious work on a CDM simulator [4] and Field-Induced CDM test methods. Thereafter, the focus on CDM rapidly increased, and IC protection methods to counter CDM started to develop. The factory control methods for CDM were also established where additional steps of controlling insulators, avoiding hard discharges, and controlling changed boards and devices are more than safe for 500 V CDM and even for 250 V CDM [5].

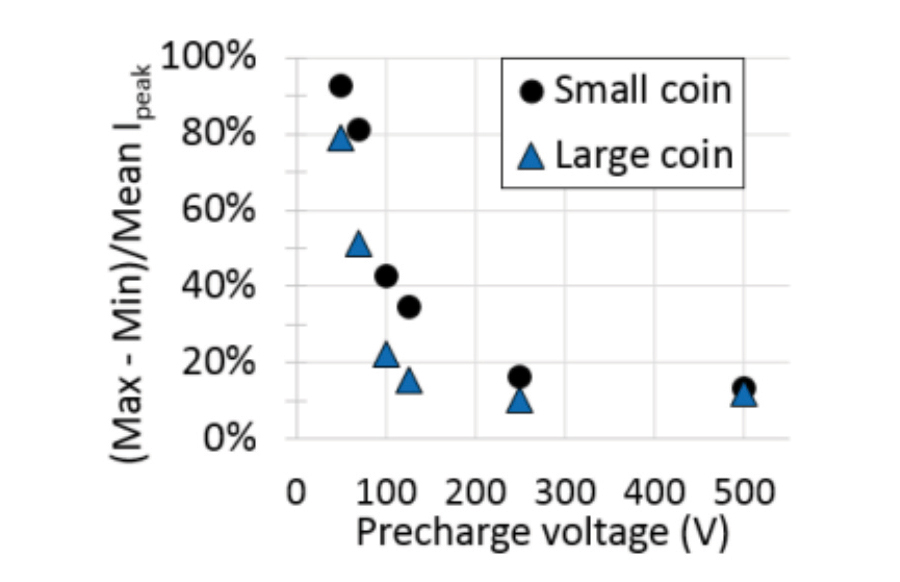

Fortunately, there are other CDM test methods in development that promise to deliver more reliable CDM test results. ANSI/ESDA/JEDEC SP5.3.3, Low Impedance Contact CDM [9] was published in 2018, which describes a contact-based method implementation of approximating the spark resistance of the field-induced method while eliminating the dependence on humidity. It has been shown to deliver repeatable, reproducible results in the 125V range and below (to 50V). Currently, the ESDA is conducting a worldwide multisite round-robin evaluation, a requirement leading to a path to a standard test method document -> inclusion as a full CDM test standard in the next 1-2 years.

Capacitively-coupled TLP (CC-TLP) [10] is another complementary method of contact mode stressing, delivering charging followed by similar CDM-like discharging, which has also been shown to be repeatable and reproducible with no dependence on humidity. A CC-TLP standard practice document is currently in review by the ESDA with a later 2021 release.

- T. Speakman, “A Model for Failure of Bipolar Silicon Integrated Circuits Subjected to Electrostatic Discharge,” Proc. of the IRPS, 1974.

- P. Bossard et al., “ESD Damage from Triboelectrically Charged Pins,” EOS/ESD Symposium, 1980.

- R. D. Enoch and R. N. Shaw, “An Experimental Validation of the Field-Induced ESD Model,” EOS/ESD Symposium, 1986.

- R. Renninger et al., “A Field-induced Charged-Device Model Simulator,” EOS/ESD Symposium, 1989.

- White Paper 2, “A Case for Lowering Component Level CDM ESD Specifications and Requirements,” http://www.esda.org/documents/IndustryCouncilWhitePaper2.pdf, alternately known as JEP157.

- White Paper 1, “A Case for Lowering Component Level HBM/MM ESD Specifications and Requirements,” http://www.esda.org/documents/WhitePaper1_HBM_MM_2010.pdf, alternately known as JEP155.

- EOS/ESD Association, ANSI/ESDA/JEDEC JS-002-2018, “Field-Induced Charged-Device Model Test for Electrostatic Discharge-Withstand Thresholds of Microelectronic Components,” 2018, available at http://www.esda.org.

- N. Jack and T. Maloney, “Low Impedance Contact CDM,” Electrical Overstress/Electrostatic Discharge Symposium Proceedings,” 2015.

- EOS/ESD Association, ANSI/ESDA/JEDEC SP5.3.3-2018, “Low-Impedance Contact CDM as an Alternative CDM Characterization Method,” 2018, available at http://www.esda.org.

- J. Weber et al, “Comparison of CDM and CC‑TLP Robustness for an Ultra-High-Speed Interface IC,” Electrical Overstress/Electrostatic Discharge Symposium Proceedings, 2018.