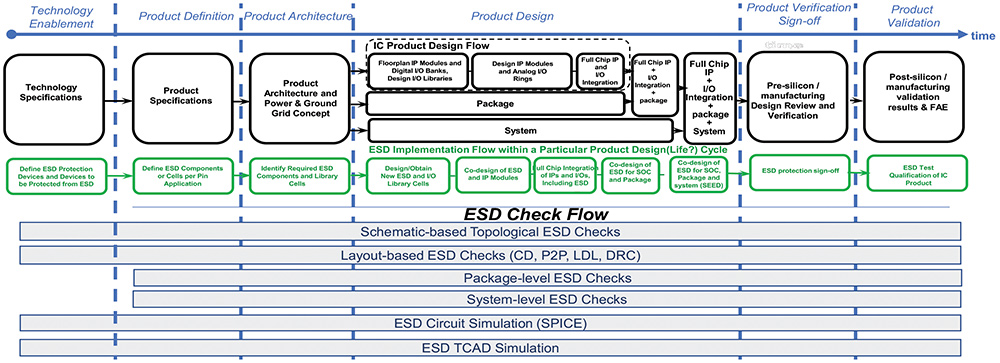

new version of Technical Report TR18.0-01-25 (TR18) on ESD Electronic Design Automation (EDA) Checks by the ESD Association’s Working Group 18 is about to be released. This article provides an overview of TR18, which offers guidelines for the EDA industry and the ESD design community to establish a comprehensive ESD verification flow. This flow addresses ESD design challenges in modern ICs, including common terminology and required check types. The main requirements are broad check coverage, manual checking limitations, transparency, and integration into the design flow for clear and actionable violation reporting. The document covers generic checks, EDA toolsets, and databases, allowing IC design companies, IDMs, or foundries to implement specific rules in their design and verification flows for automated checking.

- Technology Enablement Phase

- Product Definition Phase

- Product Architecture Phase

- Product Design Phase

- Product Verification Sign-off Phase

- Product Validation Phase

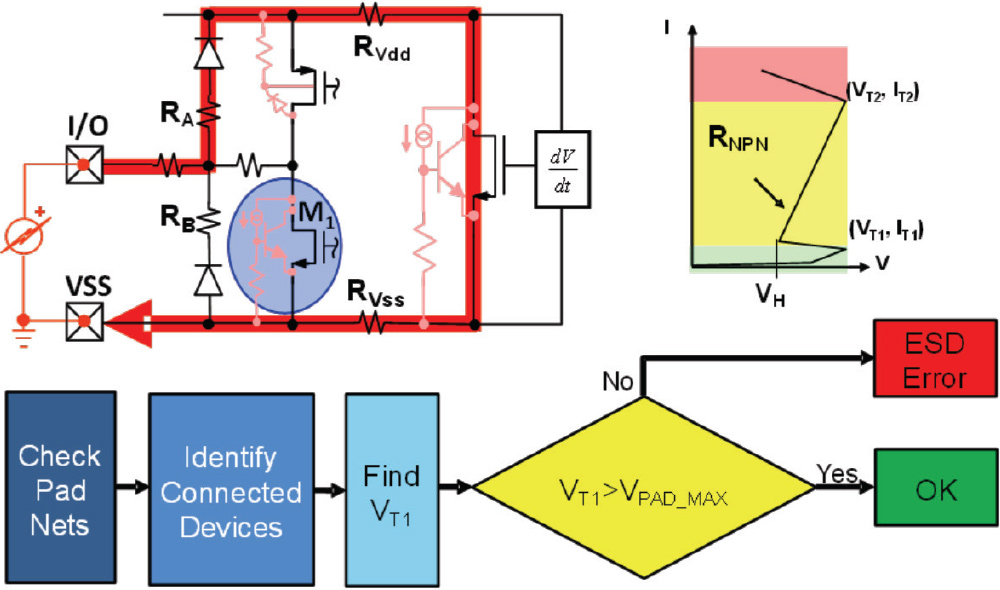

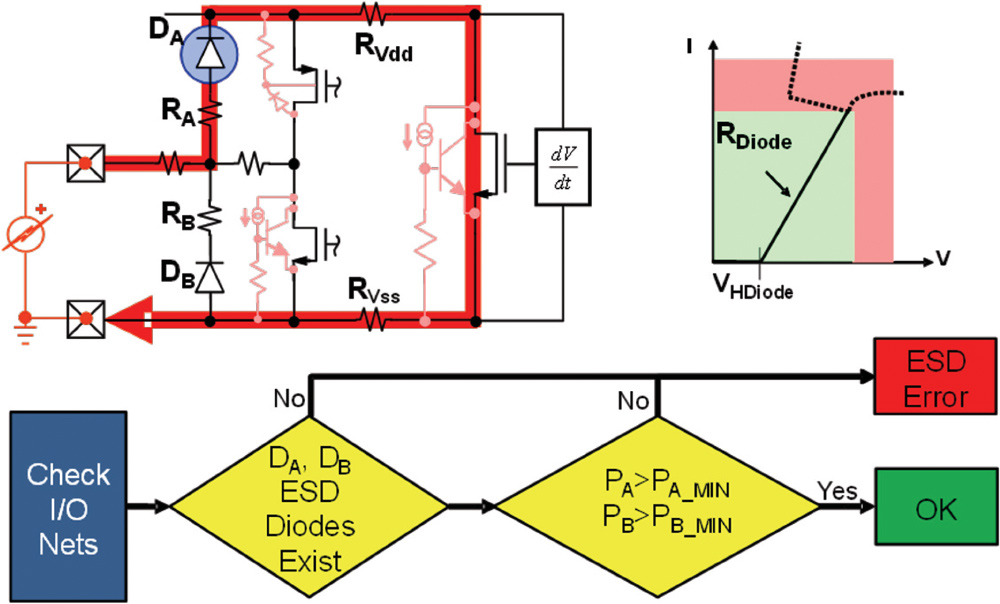

- Schematic-based Topological ESD Checks

- Layout-based ESD Checks

- Package-level ESD Checks

- System-level ESD Checks

- ESD Circuit Simulation (SPICE)

- ESD TCAD Simulation

- Geometrical Design Rule Checks (DRC)

- Logic Driven Layout (LDL) checks

- Current Density (CD) checks

- Metal routing Point to Point (P2P) resistance

In Part 2, package‑level and system-level checks sections, together with ESD circuit simulation and ESD TCAD simulation sections, will be handled, completing the coverage of all ESD EDA checks described in the Technical Report.