or 2020, TSMC is targeting to start mass production of its first 5 nm technology. Also, at this node FinFETs are the transistor architecture of choice. In this article, we will introduce FinFETs and their advantages over planar transistors. We will discuss some of the ESD protection design challenges when designing in a FinFET technology and give an outlook on the successors of FinFET.

The introduction of new gate stack materials with a higher dielectric constant than silicon oxide enabled a lower gate leakage current for the same effective oxide thickness. The scaling of the device dimensions also reduces the gate length. The short channel effect occurs if the gate length is comparable to the depletion width of the source/drain junctions. With technology scaling, the short channel effect begins to dominate. It leads to a drain-induced lowering of the barrier, the saturation of carrier velocity, and hot carrier degradation. The introduction of a three-dimensional transistor shape like FinFET provides solutions to these issues.

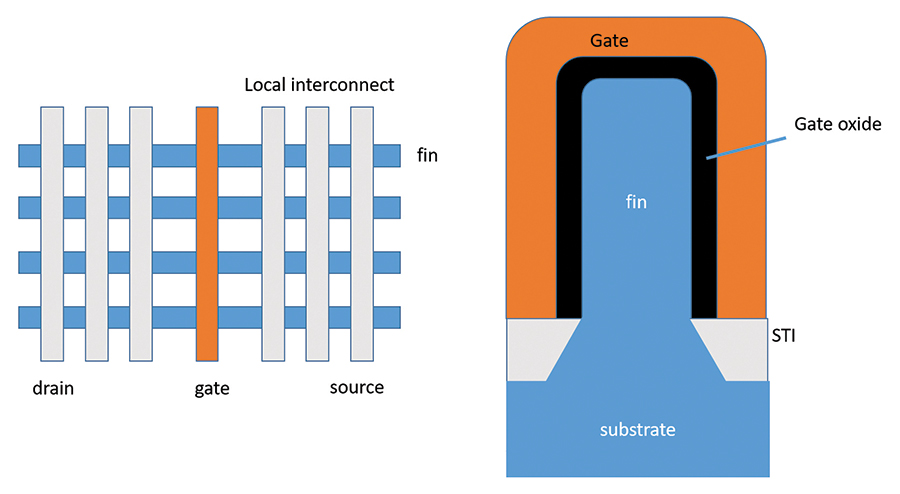

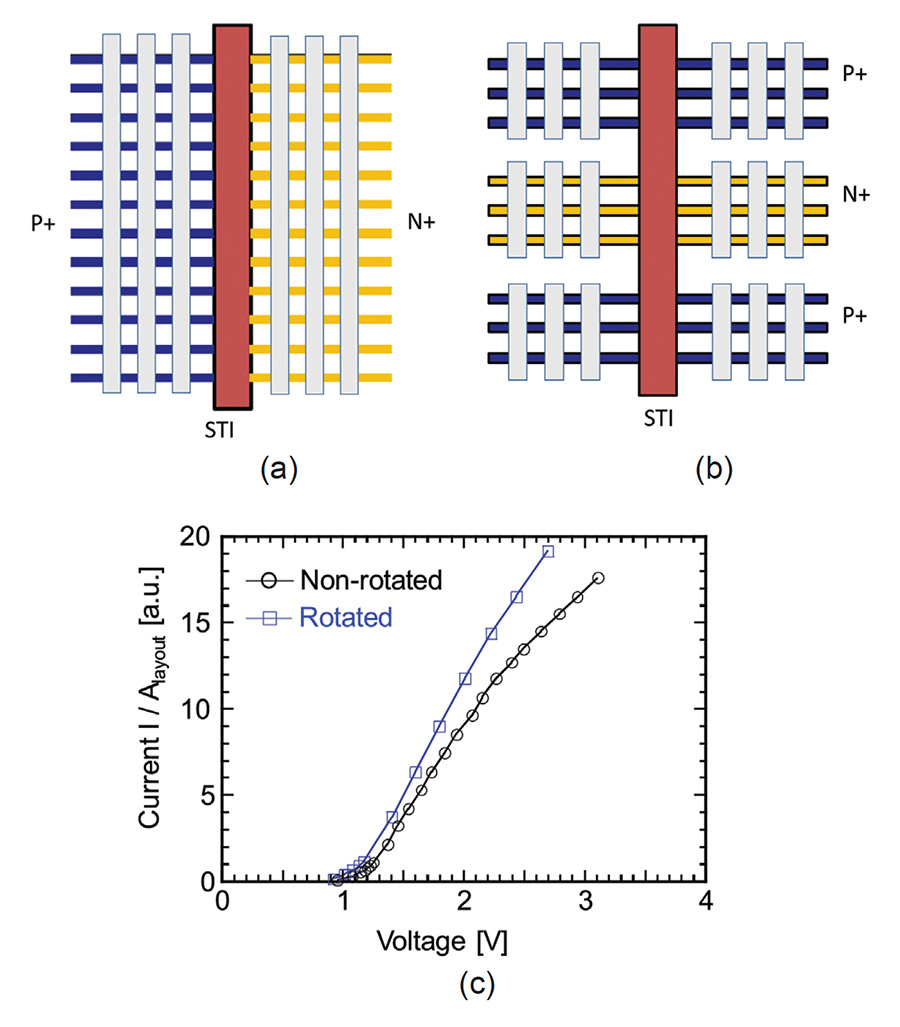

Shallow-trench isolated (STI) and gated diodes are available as ESD protection diodes. In FinFET technologies, STI diodes are more robust, with a slightly higher on-resistance (Figure 2a) and a lower capacitance (Figure 2b). In a FinFET technology, the STI is less deep than in planar technologies. Therefore, both diode types turn-on with a similar overshoot voltage during a Charge Device Model (CDM) event [2].

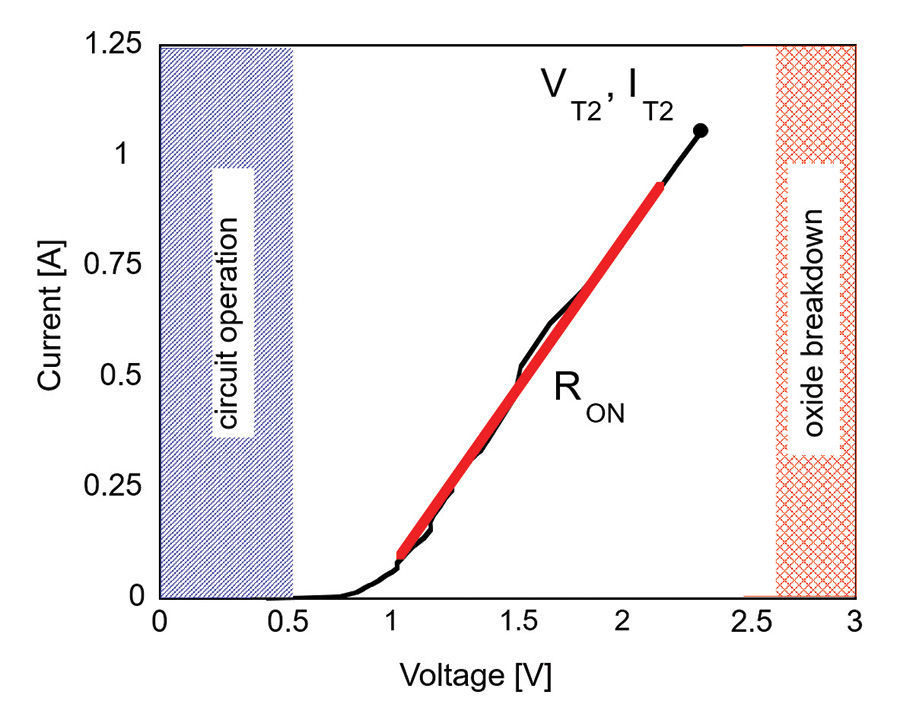

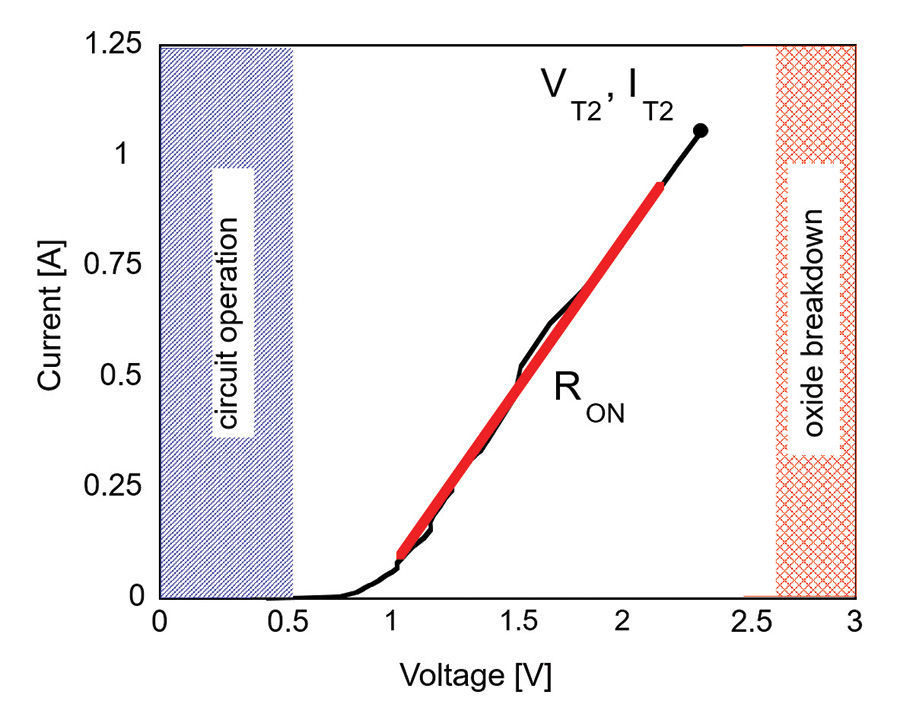

In ESD protection design, the definition of a suitable design window is an important step. In low-voltage technologies, the upper limit is the breakdown voltage of the gate-oxide (Figure 4 on page 16). Because of better gate control and less electric field across the gate stack, the breakdown voltage does not decrease in a FinFET compared to the same gate stack in a planar device [4]. This enables ESD protection design solutions that meet the ESD protection targets of the semiconductor industry.

Since their introduction, FinFET technologies have become mature technology options. Consequently, solutions for many ESD-related problems have been developed. For example, RC-triggered supply protection clamps have been developed that meet even system-level requirements [5]. The behavior of drain-extended FinFET under ESD stress has been studied. These types of transistors are used in applications where the drain voltage exceeds the supply voltage [6]. Silicon Controlled Rectifier (SCR) has been optimized to provide a low capacitance and robust CDM solution for the 7 nm node [7].

The gate around the nanowires allows improved electrostatic control of the transistor channel and device leakage current [9]. GAA NW FET can be made in a fully CMOS compatible manufacturing process. Recent work shows that ESD protection diodes in a GAA technology provide a similar ESD performance to FinFET technologies [10]. This will enable products to meet the ESD protection targets of the semiconductor industry also at the technology nodes beyond 5 nm.

![Technology nodes and their year of introduction according to the IRDS roadmap [8] (a) and comparison of the cross-section along the fin/nanowire of GAA NW FET and FinFET (b) Graphic of Technology nodes and their year of introduction according to the IRDS roadmap [8] (a) and comparison of the cross-section along the fin/nanowire of GAA NW FET and FinFET (b)](https://digital.incompliancemag.com/asset/2020/09/in-compliance-oct-2020-finfets-fig-5-new.jpg)

- “How the Father of FinFETs Helped Save Moore’s Law,” IEEE Spectrum, May 2020.

- S. Chen et al, “VFTLP Characteristics of ESD Protection Diodes in Advanced Bulk FinFET Technology,” EOS/ESD Symposium 2015

- S. Chen et al, “ESD Diodes in Sub-20nm Bulk FinFET Technology Nodes,” IEDM 2014

- S. Ramey et al, “Intrinsic Transistor Reliability Improvements from 22nm Tri-Gate Technology,” International Reliability Physics Symposium, 2013

- M. Tsai et al, “An On-chip Combo Clamp for Surge and Universal ESD Protection in Bulk FinFET Technology,” EOS/ESD Symposium 2016

- B. Kumar et al, “Physical Insights into the ESD behavior of Drain Extended FinFETs,” EOS/ESD Symposium 2017

- P.L. Peng et al, “Low-Capacitance SCR for On-Chip ESD Protection with High CDM Tolerance in 7nm Bulk FinFET Technology,” EOS/ESD Symposium 2019

- International Roadmap for Devices and Systems, 2017

- H. Mertens et al, “Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates,” VLSI Symposium 2016

- S. Chen et al, “ESD diodes in a bulk Si gate-all-around vertically stacked horizontal nanowire technology,” IEDM, 2016