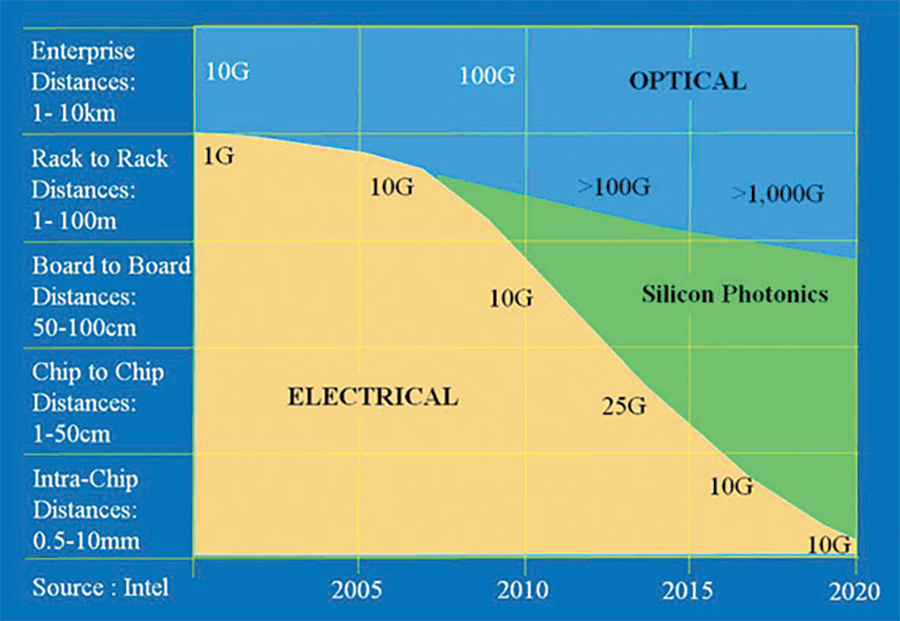

n the past, fiber-optic communication was used primarily for long-distance communication (50 km and beyond). Only a limited number of these high-end interface products were required worldwide. More recently, companies running large data centers (Facebook, Google, Amazon) have been replacing the traditional copper cabling between server racks (Figure 1). The copper-based approach is considered a bottleneck for further improvements in data transfer capacity. Optical communication can dramatically increase the bandwidth between servers while reducing complexity, power consumption, and cost.

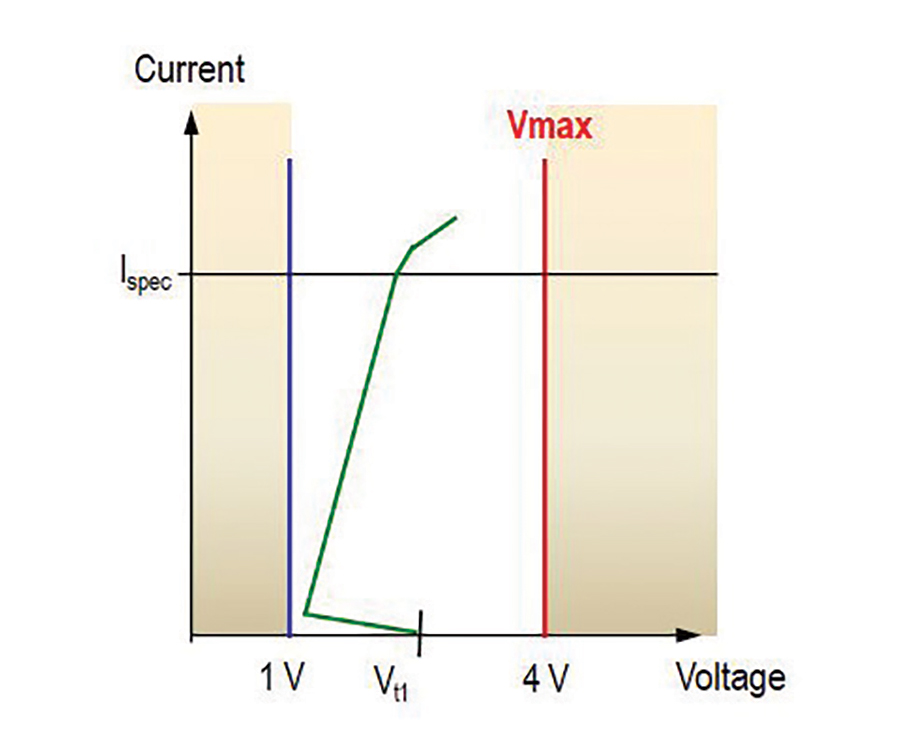

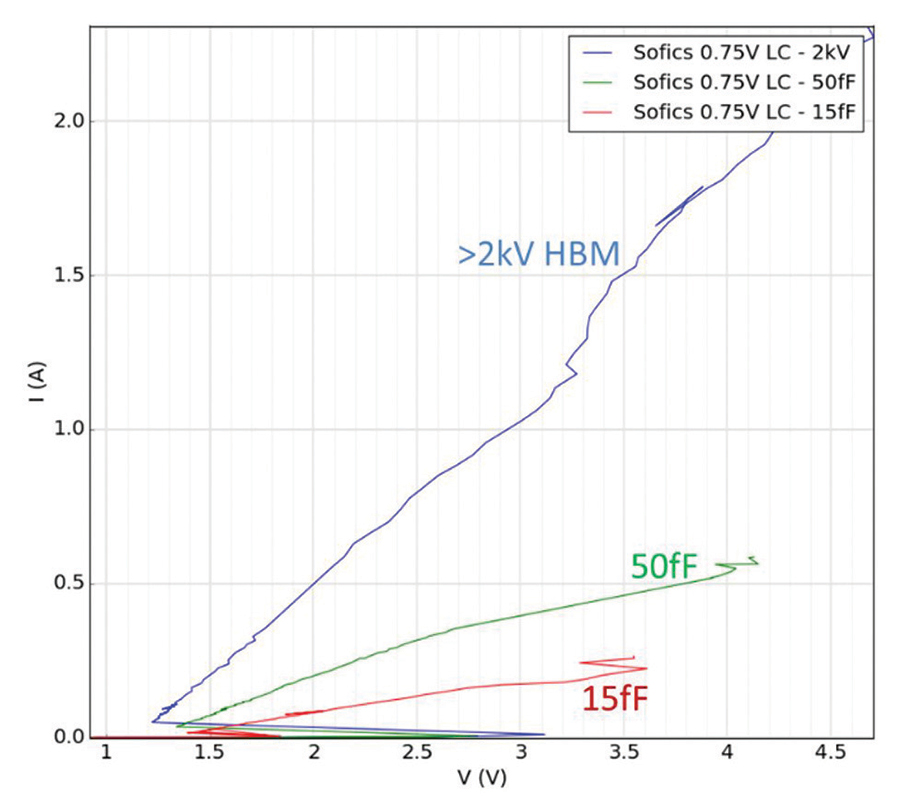

To create such high-speed differential circuits, designers utilize the thin oxide transistors. However, those transistors are very sensitive and can be easily damaged during transient events like electrostatic discharge (ESD). The maximum voltage that these transistors can endure during transient events is 4V or less.

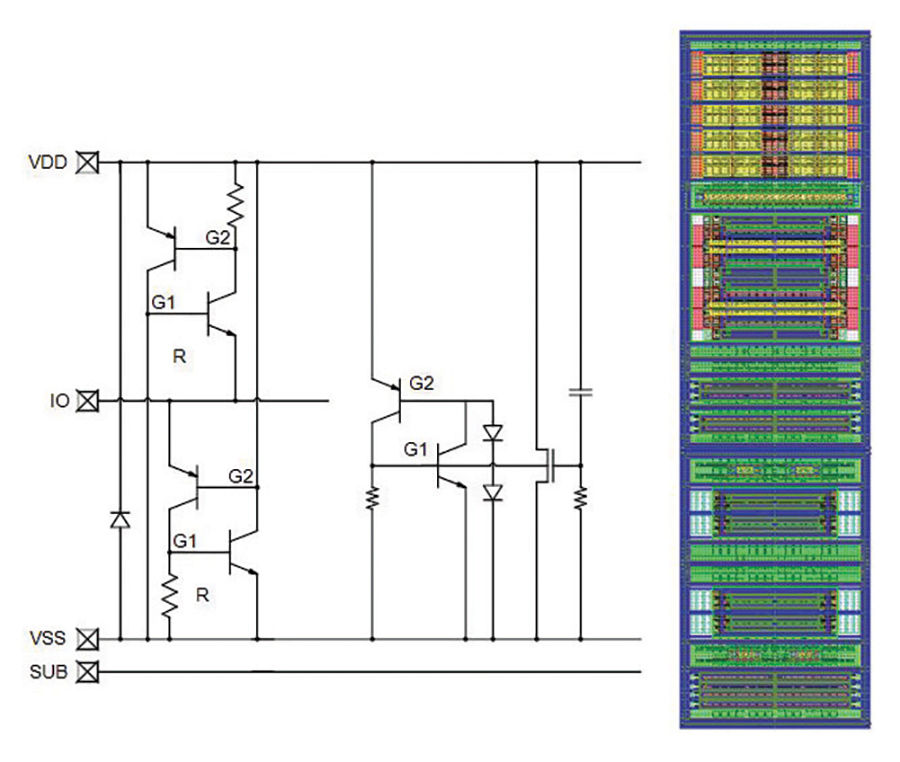

Even though the sensitive pads are not connected outside of the package, they could still receive ESD stress during assembly. Therefore, adequate protection clamps need to be inserted at the bond pads. On the other hand, for signal integrity, it is important to limit the capacitance between the interface pads and the supply lines. Selecting on-chip ESD protection with low parasitic capacitance has been studied by several authors in the past. Diode or SCR based protection concepts have been used for RF chips [4-8]. However, for the most sensitive interfaces running at low voltage, ESD protection based on dual diode at the I/O, combined with a (distributed) power clamp, is not always feasible [8].

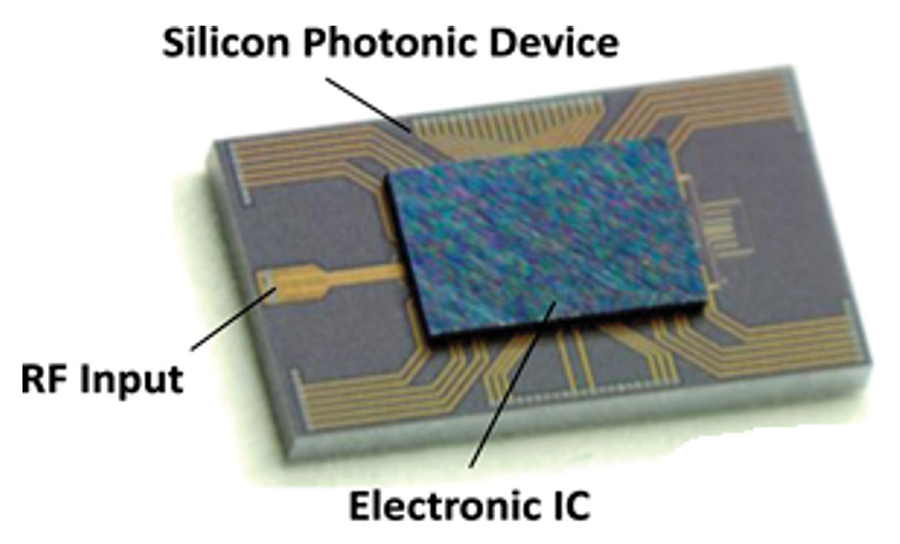

![2.5D integration of optical and electrical IC (CPU) [2] Figure 2: 2.5D integration of optical and electrical IC (CPU) [2]](https://digital.incompliancemag.com/asset/2020/08/ic-optical-img02.jpg)

Many advanced CMOS foundries provide a set of I/O and ESD protection circuits that designers can use. However, these standard, general-purpose, interface blocks are not suitable for the Silicon Photonic designs for the following reasons:

- The leakage from the general-purpose ESD blocks is too high

- The high-speed interfaces typically operate at a voltage level below the standard I/O voltage levels (1.0V or lower compared to 1.8V, 2.5V or 3.3V for the IO circuits)

- The high-speed SerDes circuits cannot tolerate a lot of parasitic capacitance or resistance added to the signal path. A typical analog I/O introduces 150fF of parasitic capacitance, well above what can be tolerated by the circuit.

Companies developing optical communication products are looking for improved solutions for the protection of the high-speed interfaces (Tx, Rx), and the low voltage power pads on the electronic die. Two case studies are included below.

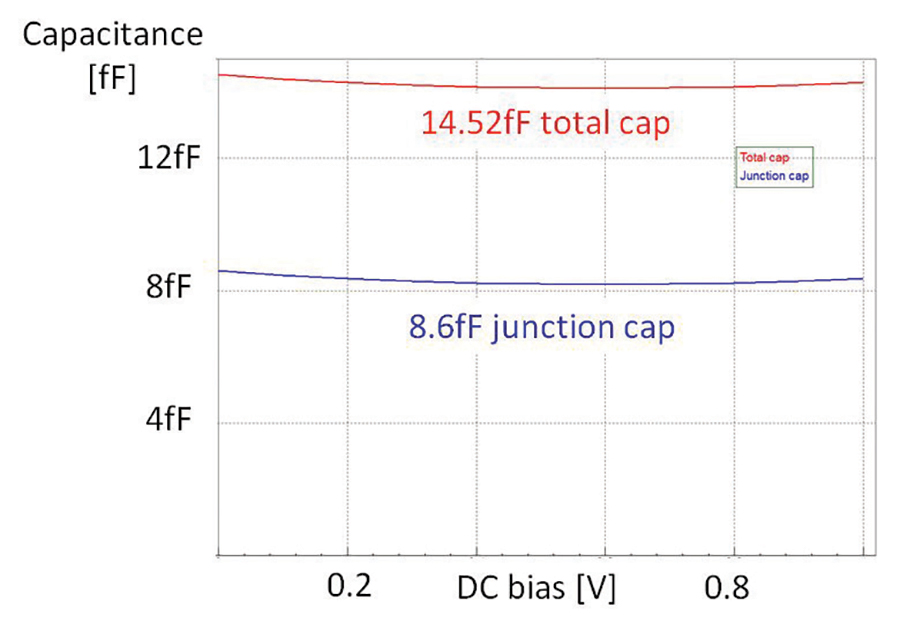

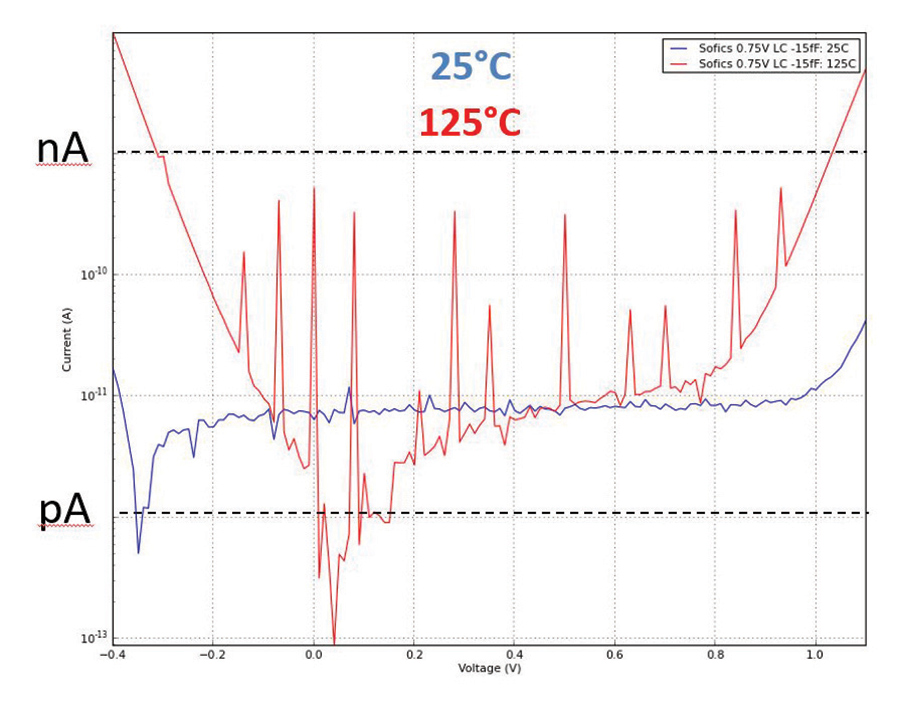

The 28Gbps interfaces used a differential pair concept. The 1V functional circuit is created using 0.9V core transistors to ensure the switching speed can be reached. However, these transistors are very sensitive during ESD stress. The available ESD design window (Figure 4) for the Rx, Tx signals is reduced to 4V. Other requirements for the ESD protection included low leakage operation and small silicon footprint (right side of Figure 5). The leakage at 1V bias is below 50pA at room temperature and less than 50nA at 125°C.

The ESD protection design consists of a full local protection clamp concept (Figure 5 on page 15). A 1V power clamp was integrated to ensure all the stress cases could be handled locally at the interface, and bus resistance is taken out of the equation. The entire clamp structure was isolated from the substrate to reduce noise from the substrate that could come from digital circuits further on the die.

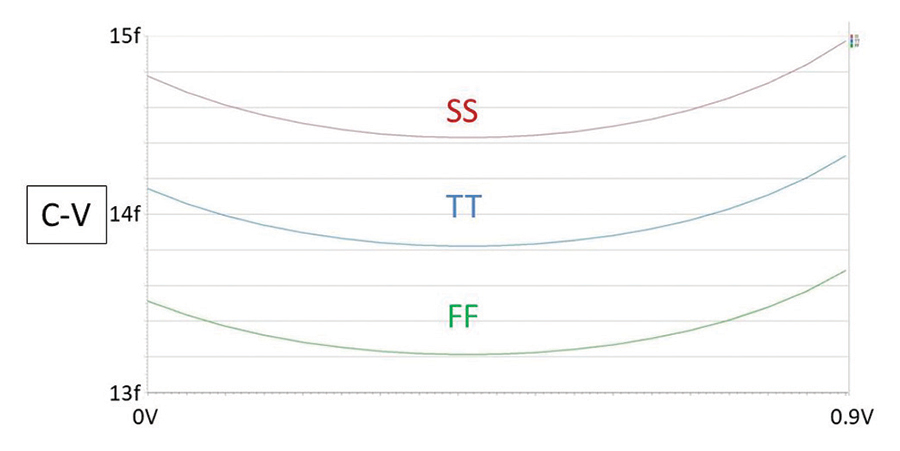

The total parasitic capacitance at the I/O pad consists of different aspects. The junction capacitance can be easily derived from the foundry provided Spice models for diodes. The metal connections to the local ESD clamps can add a significant amount of capacitance. The parasitic metal capacitance can be derived from PEX (parasitic extraction) calculations. Reducing the width of the metal connections can reduce the capacitance but will also reduce the robustness of the connection. The minimal metal width is derived from ESD stress performed at different metal stripes on our ESD test chip. Metal dummies (a requirement for CMP in advanced processes) are included in the PEX extraction when customers request ESD protection with ultra-low capacitance (well below 100fF).

In the iterative process to reduce the contribution of the parasitic capacitance from the metal connections, a number of rules are used:

- Remove unnecessary via connections

- Reduce Metal 1 as much as possible, keep it on top of the connected diffusion only.

- Prevent running Metal 1 across junctions.

- Vertical connection to higher-level metal layers to reduce capacitance from intermediate metal levels

Even when reduced, more than 40% of parasitic ESD capacitance can be linked to the metal connections in advanced nodes.

In 7nm technology, the failure voltage of core transistors (gate to source and drain to source) is about 3V. Fortunately, in many SerDes applications, there is a bit more margin due to other transistors connected in series. Failure voltage under ESD conditions of those circuits is around 4-5V depending on the circuit concept – similar to the design window shown in Figure 4.

Besides low parasitic capacitance, the SCR based solution also has a low leakage, orders of magnitude lower compared to the ESD solution proposed by the foundry. The leakage measurement for the 15fF version is shown in Figure 9.

High-speed SerDes interfaces integrated with Silicon photonics products need adequate protection with minimal parasitic capacitance. In this article, we demonstrated ESD protection clamps for 28 to 56Gbps interfaces in TSMC 28nm and TSMC N7 FinFET. Record-low parasitic capacitance levels below 20fF were achieved while ESD robustness is guaranteed.

- Lisa Huff, “Silicon Photonics – Are We Past the Hype?” http://www.connectorsupplier.com, 2015

- Fujitsu press release, http://www.fujitsu.com/global/about/resources/news/press-releases/2011/0916-01.html, 2011

- D. Thomson, et al., “Roadmap on Silicon Photonics,” Journal of Optics, volume 18, # 7, 2016.

- M.K. Radhakrishnan, et al., “ESD Reliability Issues in RF CMOS Circuits,” 2001.

- Feng K., et al., “A comparison study of ESD protection for RFICs: performance versus parasitic,” IEEE RFI, 2000.

- RMD.A Velghe et al., “Diode Network Used as ESD Protection in RF Applications,” EOS/ESD Symposium, 2001.

- K. Bhatia et al., “Layout Guidelines for Optimized ESD Protection Diodes,” EOS/ESD Symposium, 2007.

- G. Boselli, et al., “Analysis of ESD Protection Components in 65nm CMOS: Scaling Perspective and Impact on ESD Design Window,” EOS/ESD Symposium, 2005.

- J. Van der Borght et al., “Protecting Photonics Where Diodes Fail: ESD Protection for 28 to 56 Gbps Interfaces in 28nm CMOS,” International ESD Workshop 2018, Belgium.