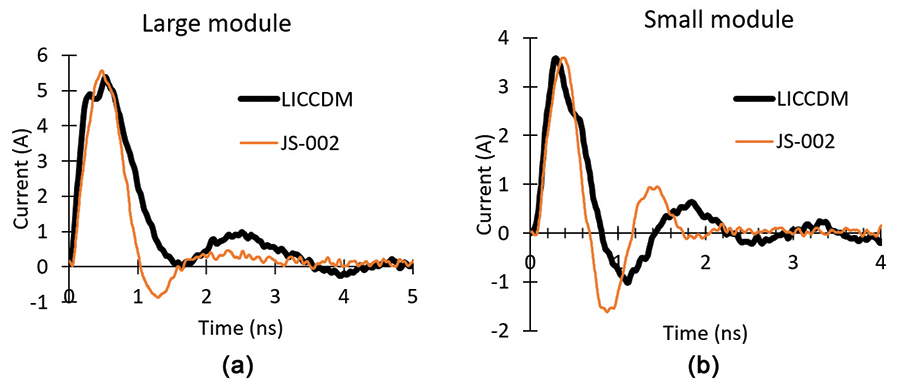

Relay-based alternatives have been proposed to eliminate the variable air spark [2], [4]. Such “contact CDM” (CCDM) systems rely on transmission line pulsing and utilize 50 Ω coaxial cables and relays. It has been shown that 50 Ω systems generate pulses much wider than those of JS-002, but a better match can be obtained using lower system impedances. In [3], CCDM systems of 50 Ω, 25 Ω, and 11 Ω impedances were demonstrated. It was theorized that a 16.6 Ω CCDM system would provide the closest match to JS-002 in terms of waveform shape and the failure current (Ifail) thresholds generated.

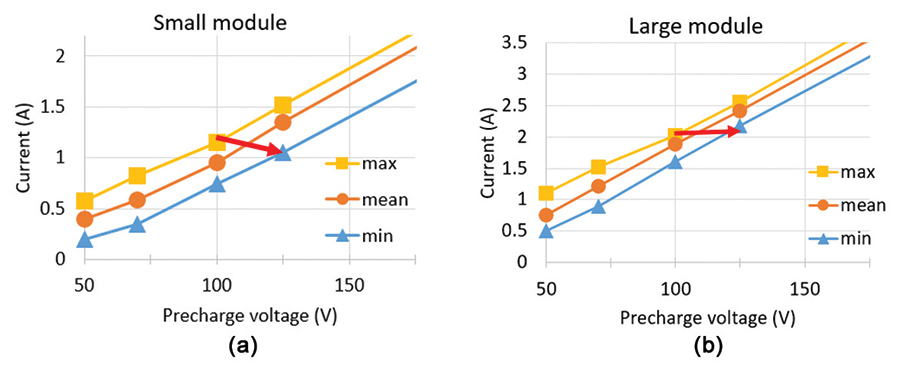

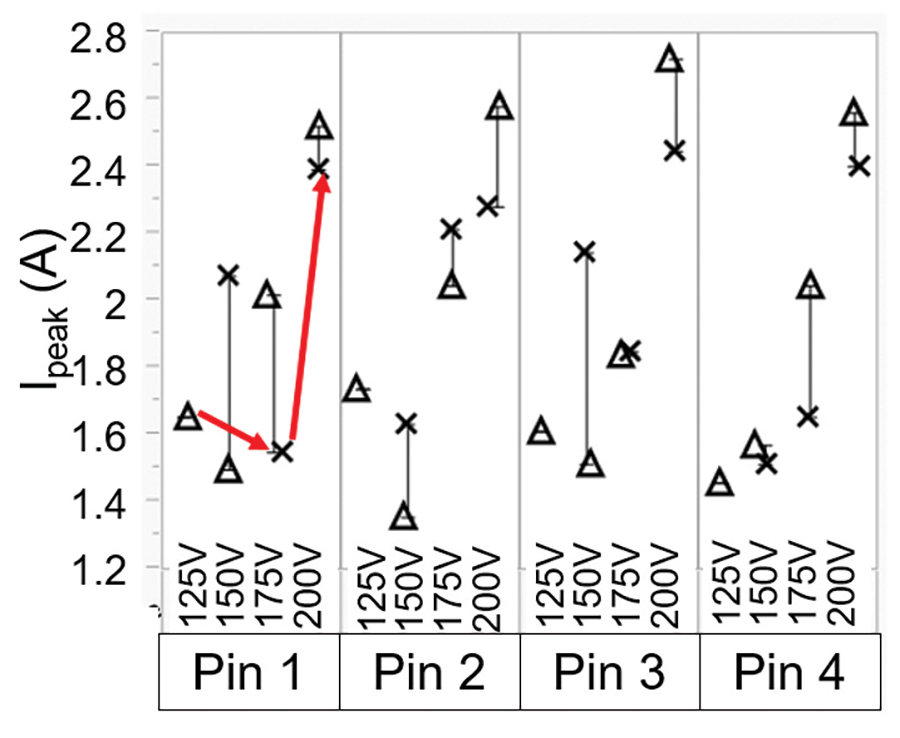

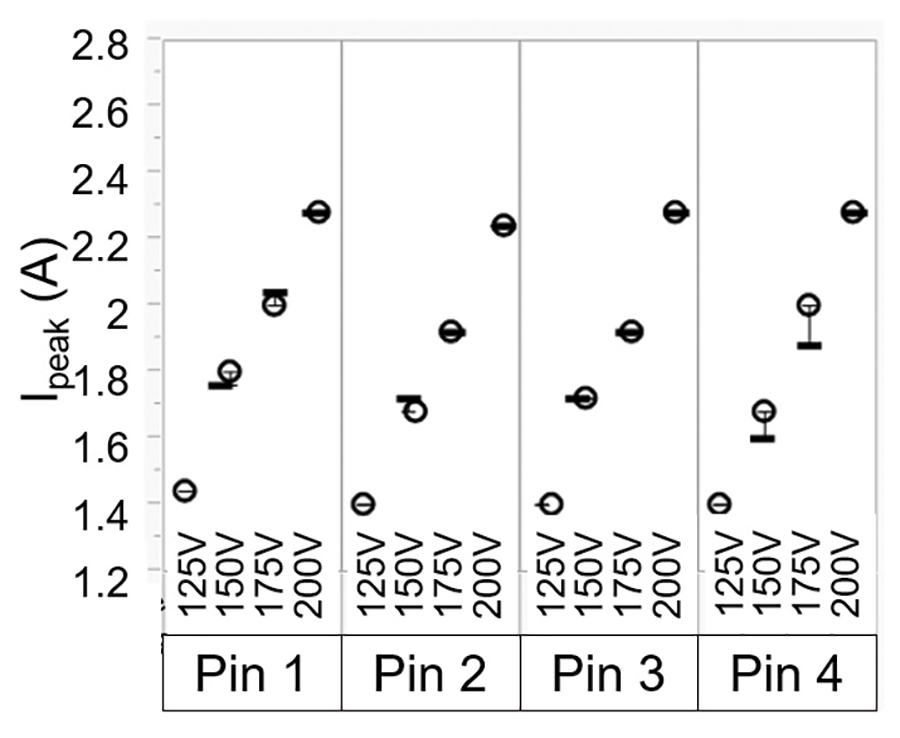

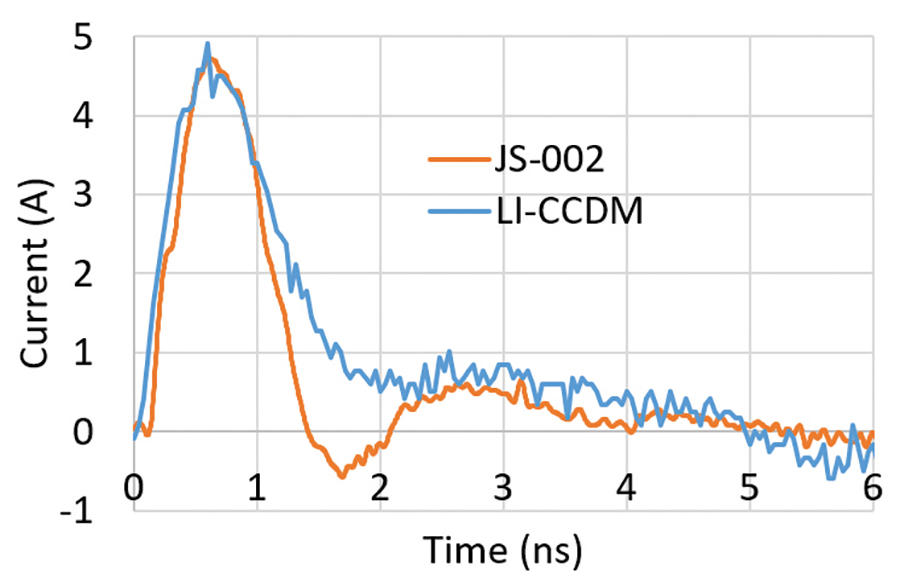

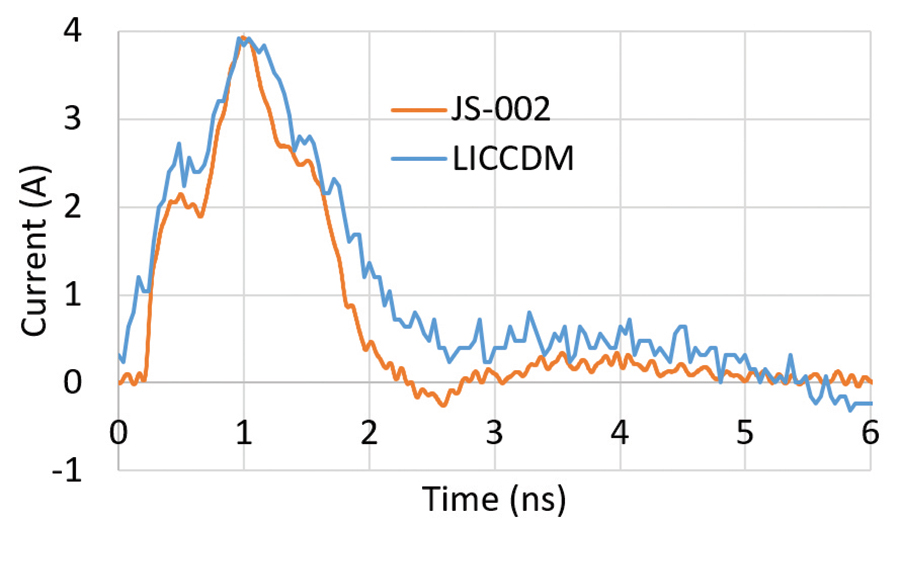

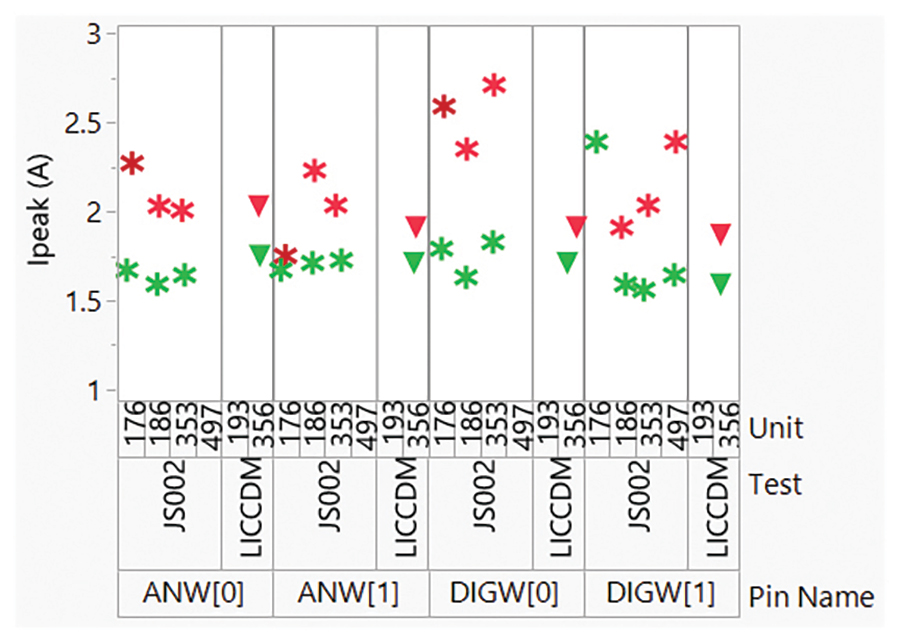

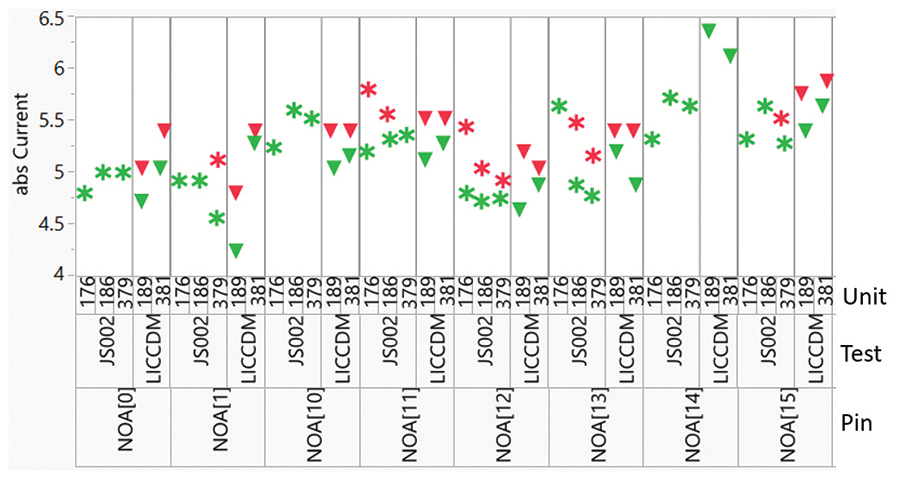

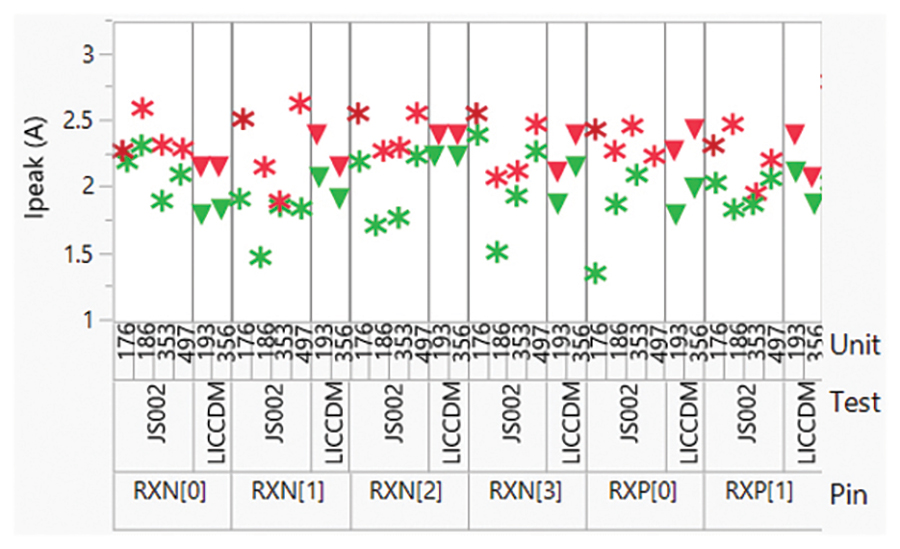

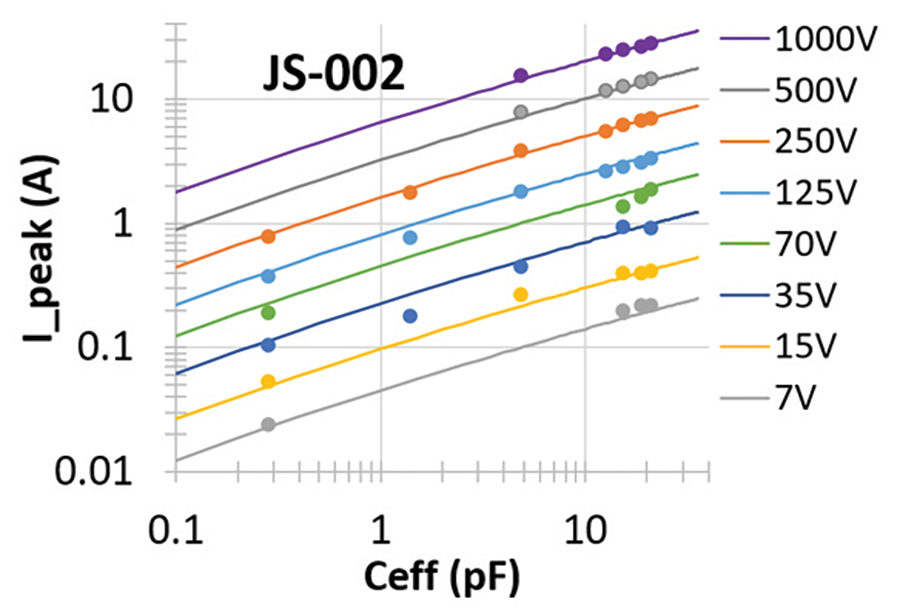

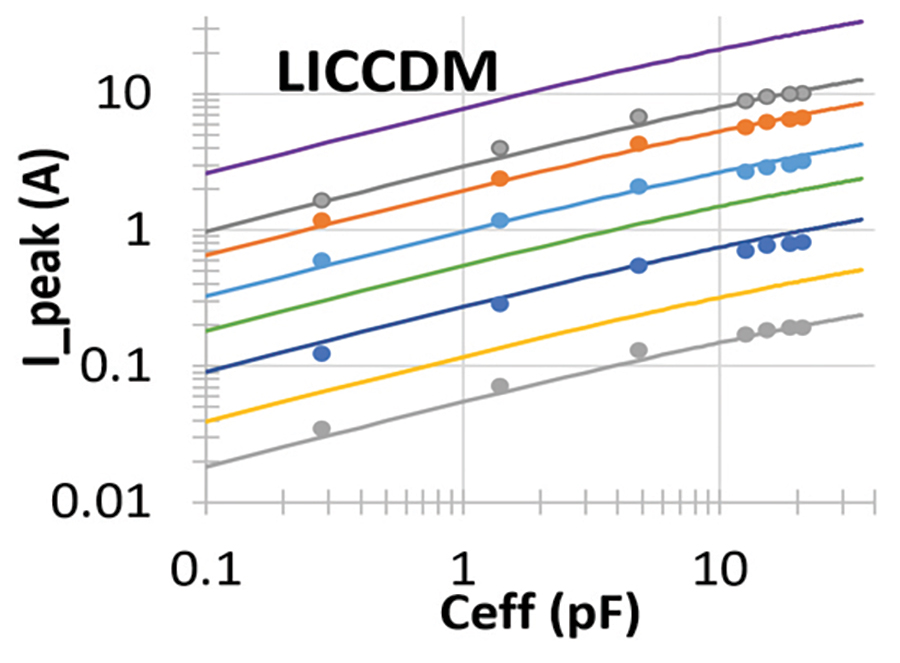

In this work, a 16.6 Ω “Low Impedance” Contact CDM system (LICCDM) is demonstrated. This system complies with the newly published CCDM Standard Practice 5.3.3 [5]. The waveform shape and Ifail threshold generated during stress of a 32 nm test chip are compared against those of JS-002. It is shown that JS-002 produces non-monotonic peak currents (Ipeak) at low Vpre. LICCDM is monotonic and enables low voltage testing with higher accuracy. LICCDM and JS-002 are shown to exhibit the same Ipeak dependency on the effective device capacitance Ceff. Recommendations for merging JS-002 and LICCDM in a future standard are proposed.

The models from Figures 14-15 are overlaid in Figure 16. The JS-002 standard has an Ipeak tolerance specified for two coin sizes at discrete “Test Conditions” (TCs) of 125 V and upward. These are indicated on the plot by solid black lines. The 1000 V, 250 V, and 125 V model curves from Figure 14 are thickened and shaded in Figure 16. The thickness represents the allowed JS-002 tolerance if it were extended across the entire Ceff range. While LICCDM (solid thin lines) is slightly less dependent on Ceff than JS-002, it can generate Ipeak within the allowed JS-002 Ipeak tolerance using a set Vpre.

Next, device level testing on a range of product applications and technologies should be conducted at multiple companies using both test methods. Failure mechanisms, locations, and Ipeak should be compared. While many CDM-induced device failures are driven by Ipeak, others are driven by pulse rise time. Recent works have highlighted this as a potential source of miscorrelation when using relay-based alternative CDM test methods. In [11] it was postulated that a very fast-rising event occurs during air discharge testing as the capacitance between the pogo pin and the ground plane charges. This rapid event is not accurately measured by the disk resistor but was shown to be the likely cause of failure on a sensitive product. Relay-based methods were only able to replicate this failure by generating sub-100 ps rise times. The same was true in [12]; a miscorrelation between air discharge and relay-based Capacitively Coupled TLP (CC-TLP) was only resolved with sub-100 ps rise times. LICCDM and CC-TLP can generate these fast rise times, but it complicates the hardware setup. Given that the sub-100 ps rise time is not accurately measured on JS-002 today, relay-based testers like LICCDM and CC-TLP actually offer a more accurate alternative. A broader product study can help the industry decide how crucial it is to replicate these rapid rise time events and what the correct waveform would look like.

- Keep the existing JS-002 small / large verification module Ipeak + tolerance limits as-is. Add a third very small verification module (with corresponding limits) to be verified before testing very small devices.

- Verify the tester by essentially following the JS-002 procedure. As is typical today with JS-002, the actual Vpre will not match the TC voltage. The software would apply a single scale factor to adjust Vpre such that the Ipeak requirements are satisfied for all three modules. For LICCDM, this scale factor would be larger (approximately 3x) because Vpre is applied to the charge cable.

- Specify the pertinent details of the waveform shape. It may be necessary to specify the rise time and pulse widths at multiple points (e.g., specify pulse width at 20%, 50%, and 80%). Product level correlation studies will inform these decisions.

- Specify a TC above which either LICCDM or air discharge methods can be used. Below this TC, only LICCDM (or a similar relay-based tester compliant to #1 – #3 above) should be used to avoid significant variability.

- Report the results in terms of the legacy Test Condition voltage. The Ipeak = f (Vpre, Ceff) continuous function could optionally be published to inform users of the expected Ipeak at any TC for a given Ceff.

- “Charged Device Model (CDM) – Device Level”, ANSI/ESDA/JEDEC, JS-002, 2018.

- R. Given, M. Hernandez, and T. Meuse, “CDM2 – A New CDM Test Method for Improved Test Repeatability and Reproducibility,” Proc. EOS/ESD Symp., 2010, pp. 359-367.

- N. Jack and T. Maloney, “Low Impedance Contact CDM,” Proc. EOS/ESD Symp., 2015.

- H. Wolf, H. Gieser, W. Stadler, and W. Wilkening, “Capacitively coupled transmission line pulsing CC-TLP—A traceable and reproducible stress method in the CDM-domain,” Proc. EOS/ESD Symp., 2003.

- “Low Impedance Contact CDM as an Alternative CDM Characterization Method,” ANSI/ESD, SP5.3.3-2018.

- T. Brodbeck, K. Esmark, and W. Stadler, “CDM Tests on Interface Test Chips for the Verification of ESD Protection Concepts,” Proc. EOS/ESD Symp., 2007, 1A.1.

- J. Di Sarro, B. Reynolds, and R. Gauthier, “Influence of package parasitic elements on CDM stress,” Proc. EOS/ESD Symp., 2013, 9A.3.

- “Field-induced charge-device model test method for electrostatic discharge withstand thresholds of microelectronic component,” JEDEC, JESD22-C101F, 2013.

- Industry Council on ESD Target Levels, May 2016, “White Paper 2: A case for lowering component level CDM ESD specifications and requirements.”

- R. Ashton, M. Johnson, S. Ward, “CDM Testing of Small Integrated Circuits,” In Compliance Magazine, June 2010.

- D. Johnsson, K. Domanski, and H. Gossner, “Device Failure from the Initial Current Step of a CDM Discharge,” Proc. EOS/ESD Symp., 2018.

- J. Weber et al., “Comparison of CDM and CC-TLP Robustness for an Ultra-High Speed Interface IC,” Proc. EOS/ESD Symp., 2018.

Brett Carn is a principal engineer at Intel and can be reached at brett.w.carn@intel.com.

Josh Morris is an ESD engineering technician at Intel and can be

reached at josh.p.morris@intel.com.