Latch‑up Survey

n July 2020, the Industry Council on ESD Target levels, in collaboration with the JEDEC JESD78 working group, launched a survey on latch-up testing. As described in an earlier article [1] in this magazine, the survey was conducted to better understand how the present latch-up standard (JESD78 revision E) is interpreted and used in the industry. The article also invited representatives from the industry to participate in order to collect data and opinions. The survey is closed, but a pdf version is still available at https://www.esdindustrycouncil.org/ic/docs/latchupsurvey2020.pdf.

This article provides a high-level overview of the Industry Council paper “Survey on Latch-up Testing Practices and Recommendations for Improvements,” which describes the full analysis of the collected responses and lays a path for potential adaptations needed to accommodate its use in future technologies and applications. Based on the survey results, we summarize the key issues documented in the paper that include problems with the latch-up standard and its application. Based on that analysis, the compiled results suggest improvements for better understanding and future JESD78 related testing. This article serves explicitly as an invitation to read the published paper, which is freely available from the Industry Council website [2] and will also become available via the JEDEC website [3].

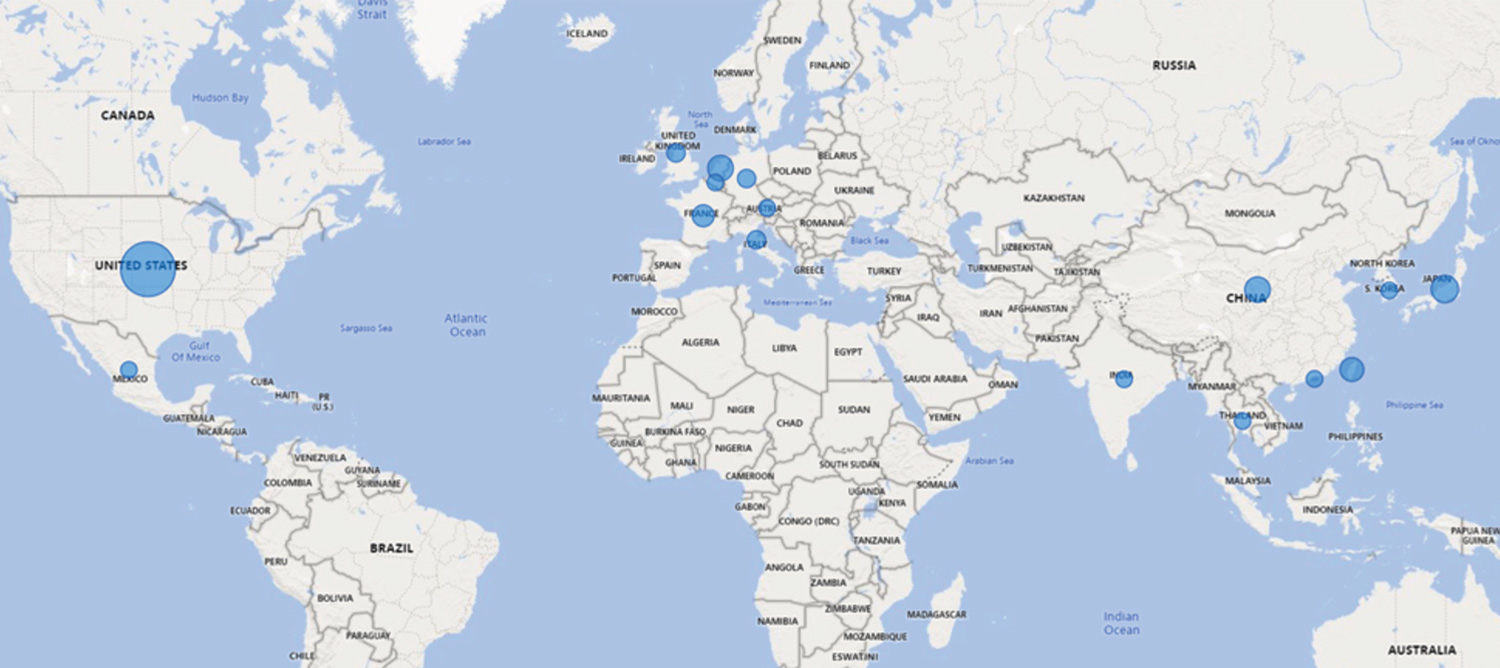

The Industry Council received 70 individual responses from at least 35 companies from more than 16 countries. The distribution over the globe is illustrated in Figure 1. Multiple responses per company were encouraged because of the wide diversity of products, customers, and requirements. This makes it likely that different approaches to latch-up testing may be used even within one company.

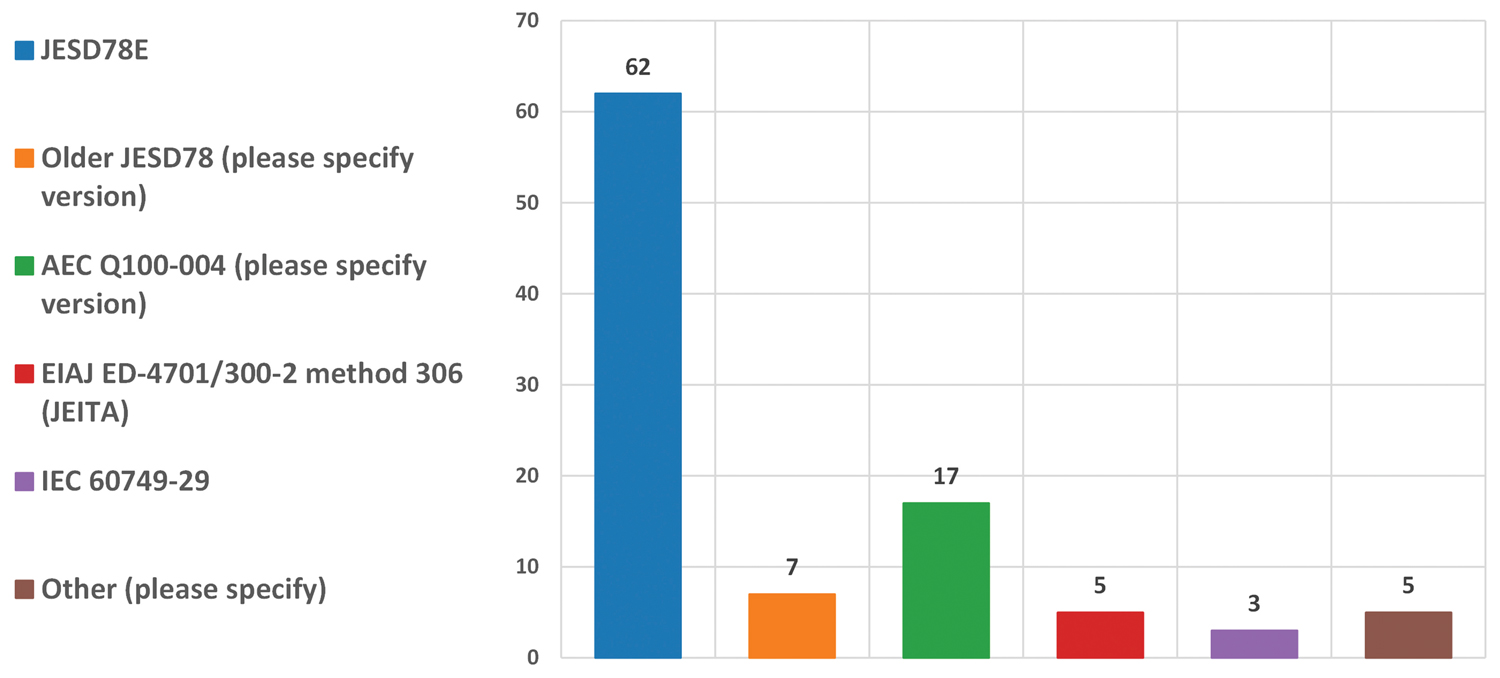

Based on questions with respect to market space, business type, and applications, we can conclude that the respondents cover the industry well. Notable exceptions are OEMs using analog ICs. Although the survey was oriented at Revision E of the JESD78 standard, it is relevant to know which standards are actually used. Figure 2 shows that although other test standards and older JESD78 revisions are also used, the most prevalent standard in use is JESD78E. This gives good confidence in the relevance of the responses with respect to the survey’s goals.

- How is the test standard interpreted and executed across the industry?

- Which real-life events does JESD78 intend to simulate? Do these occur in present-day applications?

- The prescribed voltage compliance limits prevent any significant current injection for low voltage pins. Is that intended and/or desired?

- Do we have evidence that the test method is a good predictor of robustness against latch-up in the field?

- What changes should be made to the standard to better suit the reality of present-day and future technologies and products?

- How is the test standard interpreted and executed across the industry?

- Which real-life events does JESD78 intend to simulate? Do these occur in present-day applications?

- The prescribed voltage compliance limits prevent any significant current injection for low voltage pins. Is that intended and/or desired?

- Do we have evidence that the test method is a good predictor of robustness against latch-up in the field?

- What changes should be made to the standard to better suit the reality of present-day and future technologies and products?

Chapter 2 of the paper describes the detailed analysis of the responses in relation to the questions mentioned above. An effort was made to address topics in the same sequence as the questions appeared in the survey. The analysis is meant to strictly report and summarize the respondents’ information and find potential correlations between different topics. However, whenever the analysis team felt it was appropriate to offer a “possible interpretation,” it was indicated using a special box format with the disclaimer that other interpretations would be possible.

Conclusions and Recommendations

One of the most relevant questions is if JESD78 latch-up testing ensures the robustness of products in the field. Related key findings are:

- JESD78 is considered useful and should not be removed.

- It is evident that passing JESD78 testing is insufficient to guarantee latch-up robustness in the field, as shown in Figure 3, and seems to be more related to the type of stress rather than the levels.

- Respondents see value in JESD78 testing for modeling real-world stress events beyond the specified test conditions.

- JESD78 is considered useful and should not be removed.

- It is evident that passing JESD78 testing is insufficient to guarantee latch-up robustness in the field, as shown in Figure 3, and seems to be more related to the type of stress rather than the levels.

- Respondents see value in JESD78 testing for modeling real-world stress events beyond the specified test conditions.

- Figure 4 shows the majority of latch-up fails are reported during the JESD78 qualification test, and many of these fails result in a re-spin, but this accounts for a very small fraction of the total number of re-spins as shown in Figure 5.

- More than 50% of all latch-up failures (field + JESD78 testing) do not require a re-spin, but the failure drives alternative mitigations such as board modifications or software changes

- Figure 4 shows the majority of latch-up fails are reported during the JESD78 qualification test, and many of these fails result in a re-spin, but this accounts for a very small fraction of the total number of re-spins as shown in Figure 5.

- More than 50% of all latch-up failures (field + JESD78 testing) do not require a re-spin, but the failure drives alternative mitigations such as board modifications or software changes

The last highlighted topic is the question if the standard is sufficiently clear. It appears that some concepts in the standard are not interpreted the same way by all users and sometimes are even used incorrectly. The most important example is:

- The concept of the “Maximum Stress Voltage” is well-known in the industry but very often misinterpreted or incorrectly applied to JESD78 testing

- Many respondents believe that the pin stress voltage should not exceed the product AMR, see Figure 7

- The concept of the “Maximum Stress Voltage” is well-known in the industry but very often misinterpreted or incorrectly applied to JESD78 testing

- Many respondents believe that the pin stress voltage should not exceed the product AMR, see Figure 7

- Create a JESD78 user guide with practical explanations, hints, and examples.

- Provide seminars and workshops aligned with the latest JESD78 revision F release, discussing the major changes from JESD78 revision E and its implications to LU testing.

- Consider ways to standardize LU testing at the application level (System Level ESD, Transient LU).

- Create a JESD78 user guide with practical explanations, hints, and examples.

- Provide seminars and workshops aligned with the latest JESD78 revision F release, discussing the major changes from JESD78 revision E and its implications to LU testing.

- Consider ways to standardize LU testing at the application level (System Level ESD, Transient LU).

During the development of this survey and paper, the JEDEC JESD78 working group prepared and released a next revision of the JESD78 standard. Chapter 3, Section 3.3 concludes the paper with a summary of the major differences between JESD78 revision E and JESD78 revision F and relates this to the recommendations provided.

Overall, the survey results indicate a dire need to improve the definition and understanding of the latch-up test standard and cover a broader range of applications. The Industry Council releases this paper to help focus the work to accomplish that.

- “Industry Council Launches Survey on Latch-Up,” In Compliance Magazine, July 2020, pp. 20-21.

- Website Industry Council on ESD Target Levels: https://www.esdindustrycouncil.org/ic/en

- Website JEDEC: https://www.jedec.org

![Figure 3 pie Chart of [Q41]](https://digital.incompliancemag.com/asset/2022/08/industry_council-03.jpg)

![Figure 4 Feedback to [Q12]](https://digital.incompliancemag.com/asset/2022/08/industry_council-04.jpg)

![Figure 5 pareto of [Q21]](https://digital.incompliancemag.com/asset/2022/08/industry_council-05.jpg)

![Figure 6 Distribution of Responses for [Q20]](https://digital.incompliancemag.com/asset/2022/08/industry_council-06.jpg)

![Figure 7 Pie Chart of Responses to [Q90]](https://digital.incompliancemag.com/asset/2022/08/industry_council-07.jpg)