he new connector standard USB-C includes both power delivery of current up to 20 V as well as SuperSpeed data lines. Integrated circuits (ICs) receiving signals on these data lines are very ESD sensitive. The Vbus pins in the USB-C connector are placed directly next to the SuperSpeed Tx and Rx pins, which poses the risk that the data pins can temporarily short to the supply voltage. The USB-C specification requires a mandatory AC coupling capacitor placed on the data lines in front of the IC when USB4 is used on the SuperSpeed lines. Thus, transient voltage suppressor (TVS) devices for system-level protection can be placed either behind the AC coupling capacitor or in front of it.

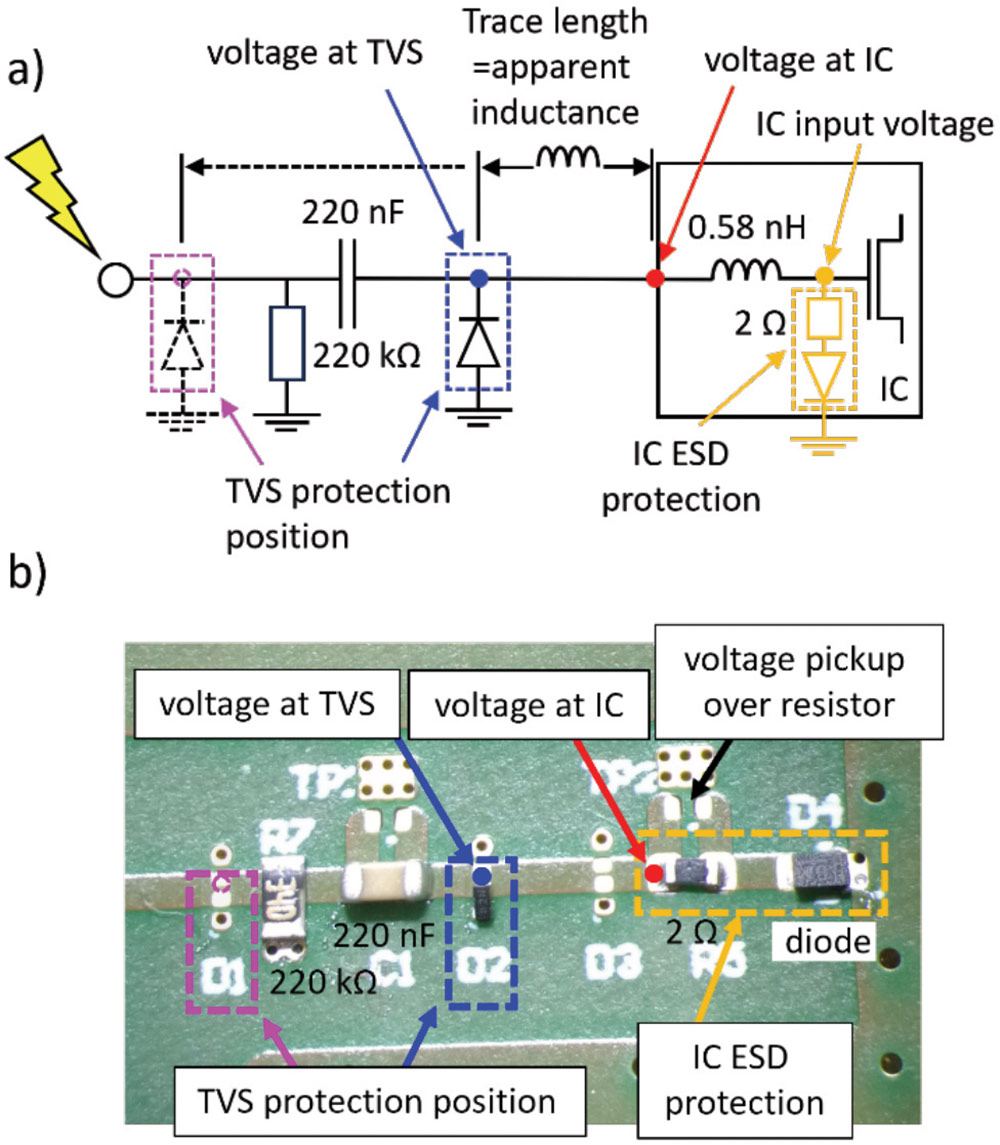

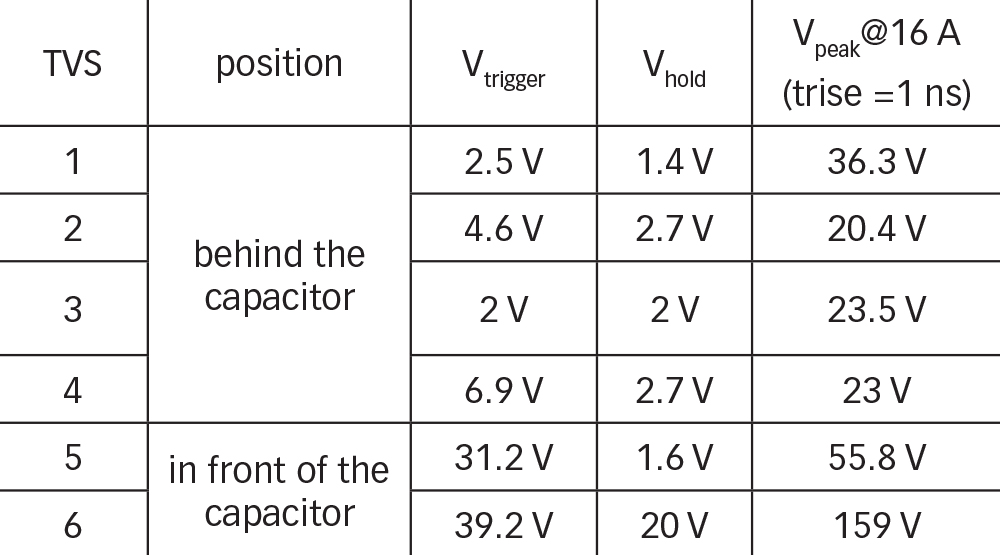

In this article, the effect of the TVS placement and the device properties on the IC is investigated. Special PCBs have been produced; one is shown in Figure 1. The distance between TVS and an IC replacement consisting of a 2-ohm resistor and a forward-bias diode is varied. The voltage at the IC can be measured. The IC residual current is determined by measuring the voltage drop across the resistor. Six different TVS protection devices have been chosen. All of them have a capacitance of less than 0.2 pF, which makes them suitable for the SuperSpeed application. Two of them are placed in front of the capacitor. However, to avoid turning on during a short to the power line, these TVS devices require a breakdown voltage larger than 20V. For a placement behind the capacitor, a high breakdown voltage is not needed. An overview of the TVS parameters is shown in Table 1.

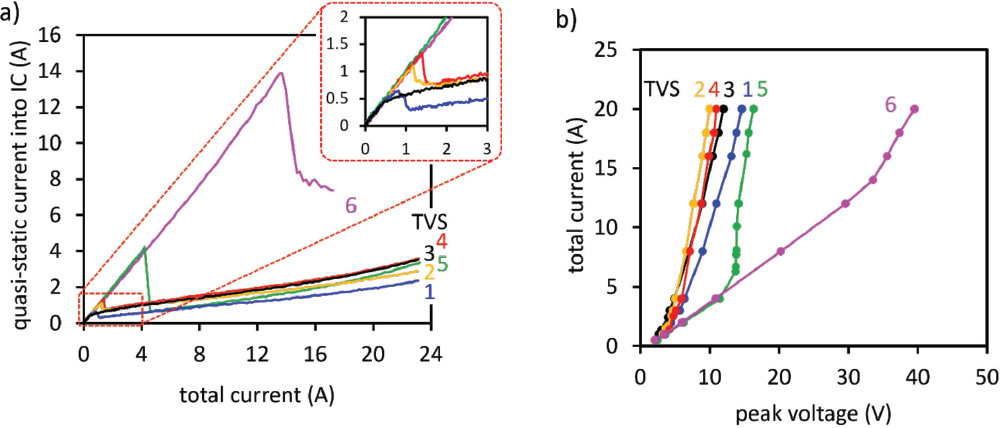

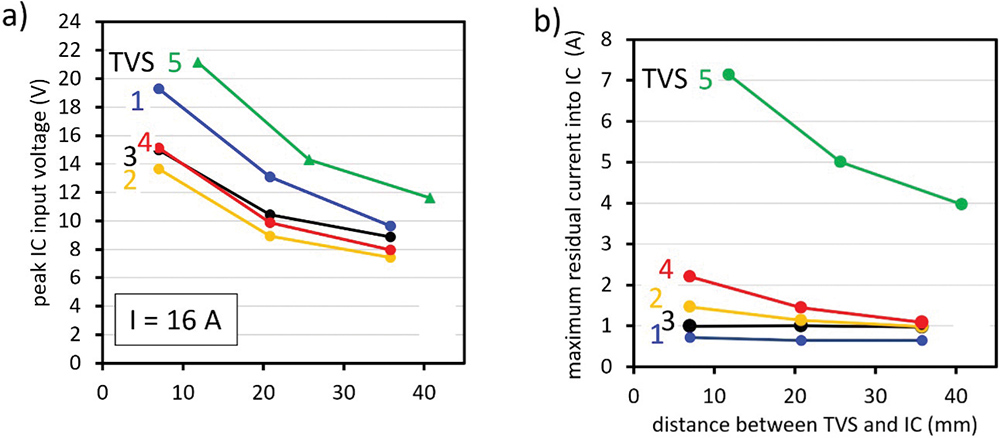

Figure 3a shows the residual current into the IC, and Figure 3b shows the peak voltage at the IC. While TVS 5 can strongly reduce the IC current after turning on, TVS 6 manages to divert only about 50% away from the IC. This is a direct effect of its high holding voltage. TVS 6 also exhibits a high peak voltage, which leads to a high peak IC input voltage. Even when the device turns on at 14 A, the peak IC input voltage is barely clamped. TVS 5 can limit the peak IC input voltage much more effectively. However, in comparison to the TVS 1 to 4 with their much lower trigger voltages, the absolute value is still higher. Compared to TVS 2, with the lowest peak IC input voltage, the value is 50% higher at 16 A. One can conclude that TVS devices with high trigger voltage, which can be placed in front of the AC coupling capacitor, would, in principle, be able to protect the capacitor. However, they are ill-suited for an effective system-level ESD protection of sensitive SuperSpeed ICs.

- S. Holland, N. Lotfi, M. Pilaski, B. Laue, and S. Seider, “Influence of TVS Properties and Printed Circuit Board Design on System Level ESD Robustness for USB-C SuperSpeed Data.”