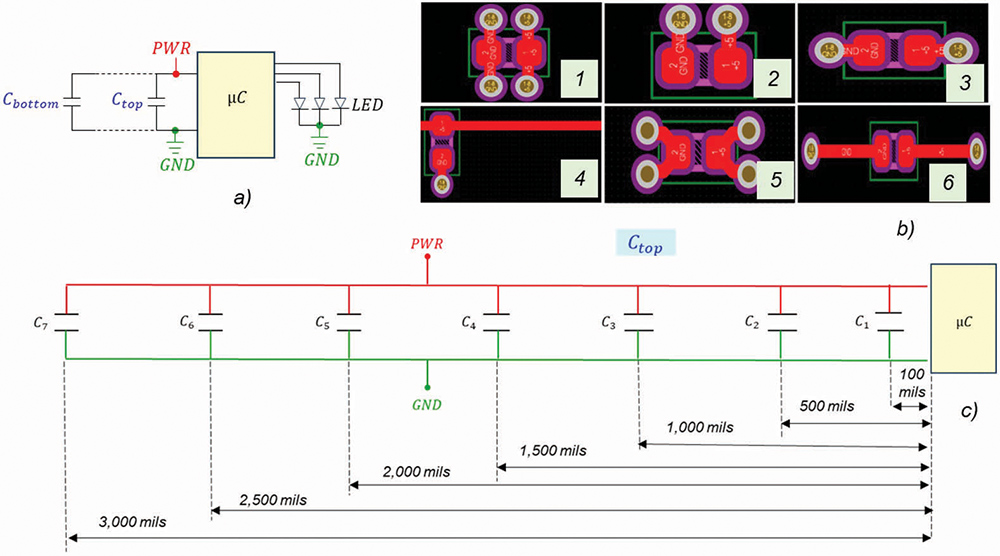

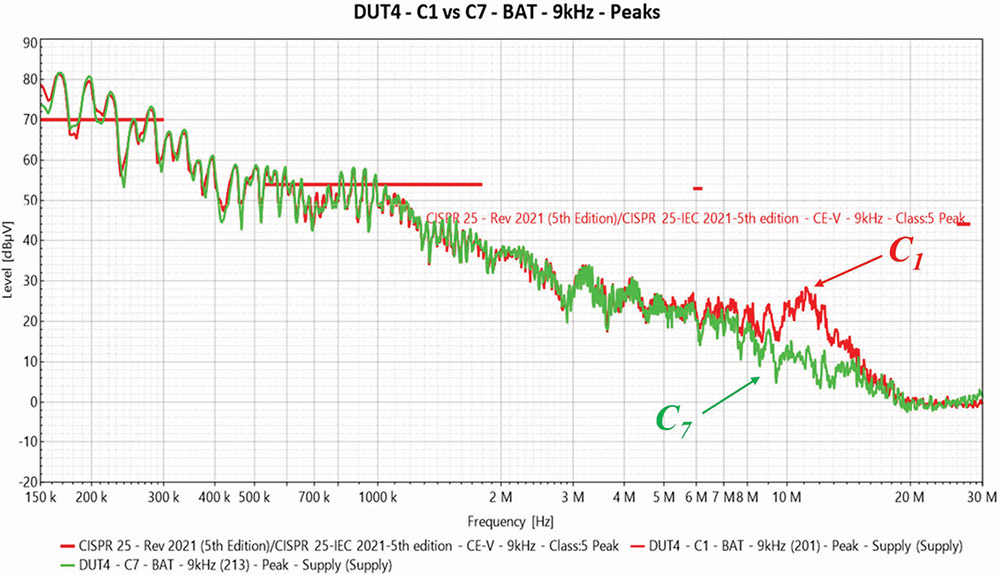

his is the second article in the series investigating the effectiveness of decoupling capacitors while varying the topology of vias, trace length between the decoupling capacitor and the IC power/ground pins, and distance from the internal power-ground plane pair. The first article, [1], introduced the PCB schematic, via and trace topologies, as well as PCB topology. This article addresses the impact of the distance of the capacitor from the IC on the conducted emissions. The IC used in the PCB design is the PIC10F200 from Microchip. This IC has an internal clock frequency of 4 MHz.

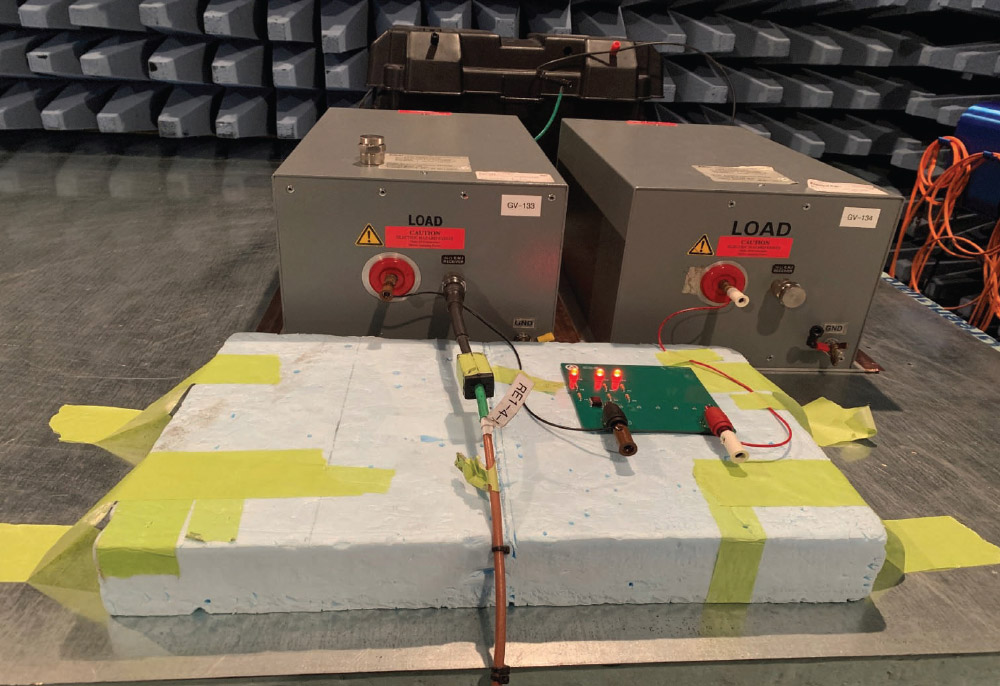

The RF Conducted Emissions of the PCB assemblies were measured on the external Power and Ground lines using the CISPR 25 (CE Voltage Method) standard setup with two Line Impedance Stabilization Networks (LISN). For the purposes of simplifying the study, the majority of the plots shown are for the Power (Battery) line. When power is applied to the IC, it toggles the LEDs on and off, rapidly using a constant rate. The purpose of switching the LEDs on and off rapidly is to create a periodic power (charge) draw, thus creating a need for proper Power Delivery Network (PDN) decoupling to reduce or eliminate conducted and radiated emissions. Note that the IC technology used in this design is bandwidth limited and its maximum edge rates and clock speed are rather slow compared to most high‑speed technologies. Therefore, there is a limit to the frequency bandwidth over which this particular IC can generate emissions from its PDN structure, and this in turn limits the frequency span over which this study is evaluated.

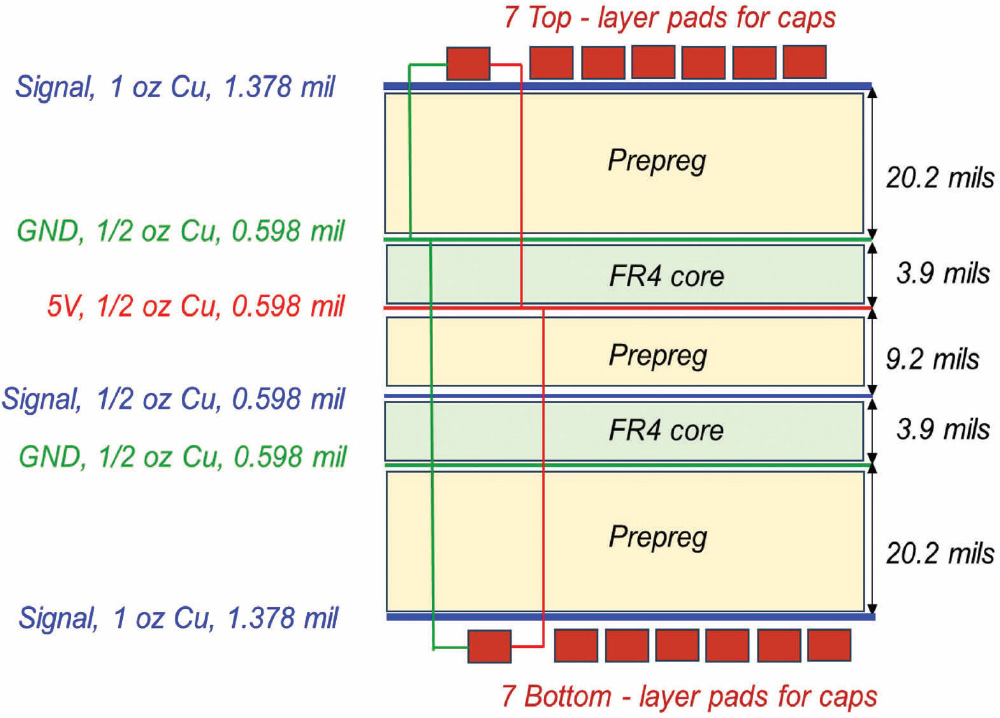

As Figure 2 shows, the top layer capacitors were closer to the internal power-ground plane pair than when placed on the bottom layer.

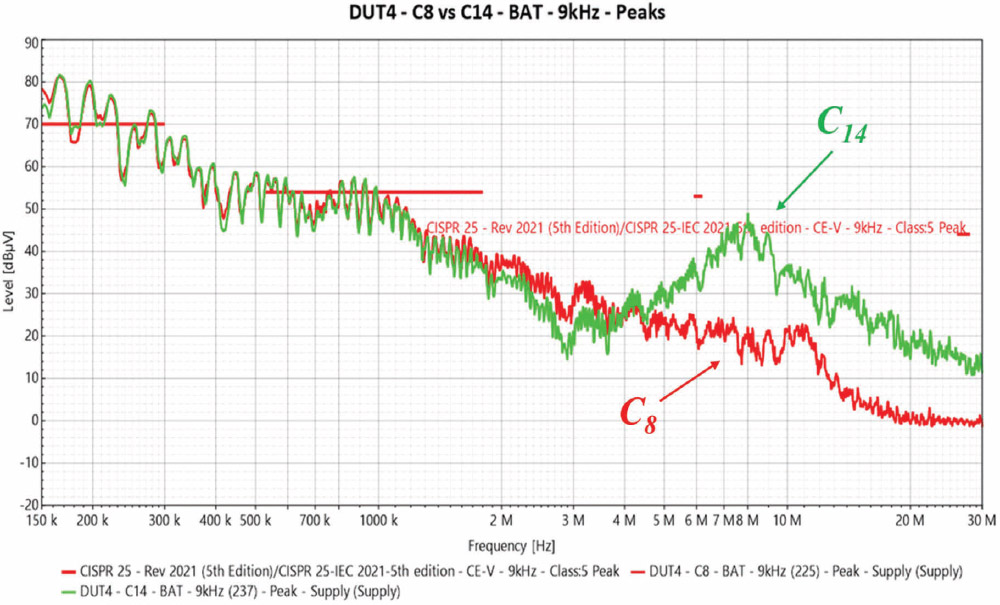

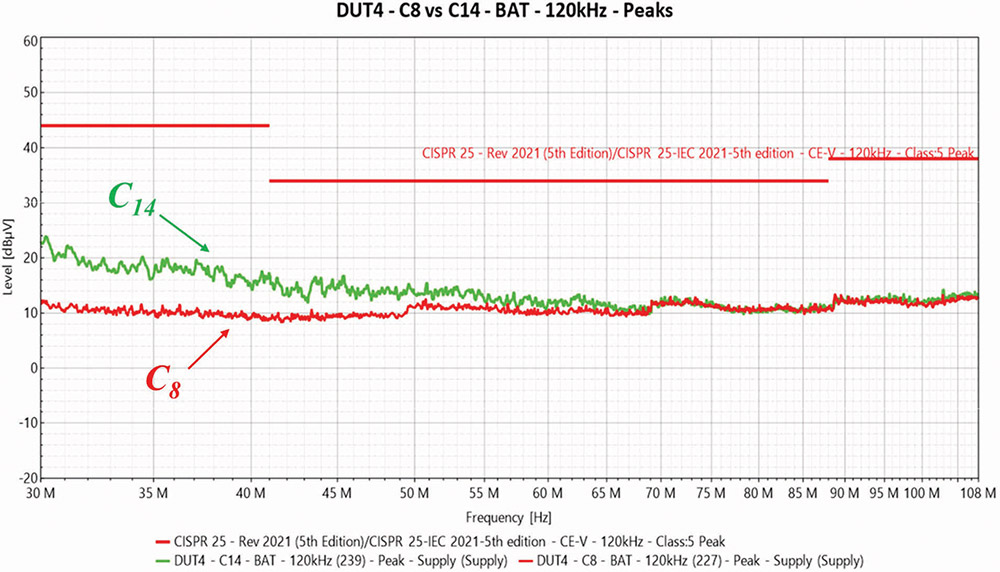

In the frequency range 30 – 108 MHz, the results for the case with the decoupling capacitor placed on the bottom side of the board showed an increase in conducted emissions over a different frequency range. Figure 7 shows the results on the battery line for C8 (location closest to the IC) versus C14 (location farthest from the IC).

- Bogdan Adamczyk, Allyson Telck, Scott Mee, “Impact of PCB Via and Trace Geometry on the Effectiveness of Decoupling Capacitors – Part 1: Board Topologies and the PCB Circuitry,” In Compliance Magazine, February 2026.