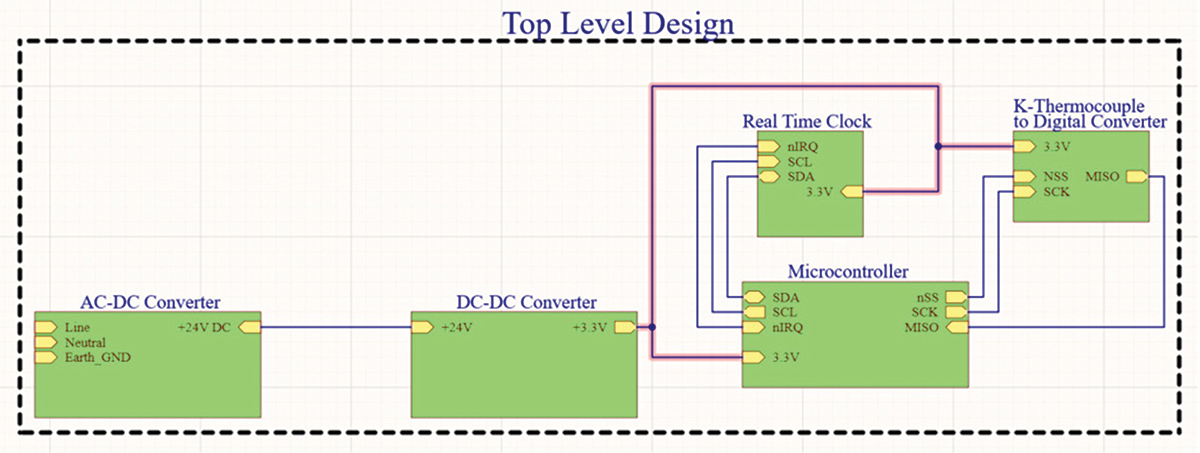

his is the second in a series of articles devoted to the design, test, and EMC emissions evaluation of 1- and 2-layer PCBs that contain AC/DC and/or DC/DC converters and employ different ground techniques [1]. In this article, we first present a top-level schematic of an overall system and then focus on a systematic approach to a DC/DC converter design. Several EMC considerations are addressed at the schematic level, and recommended design improvements are provided to reduce the risk of failures during testing.

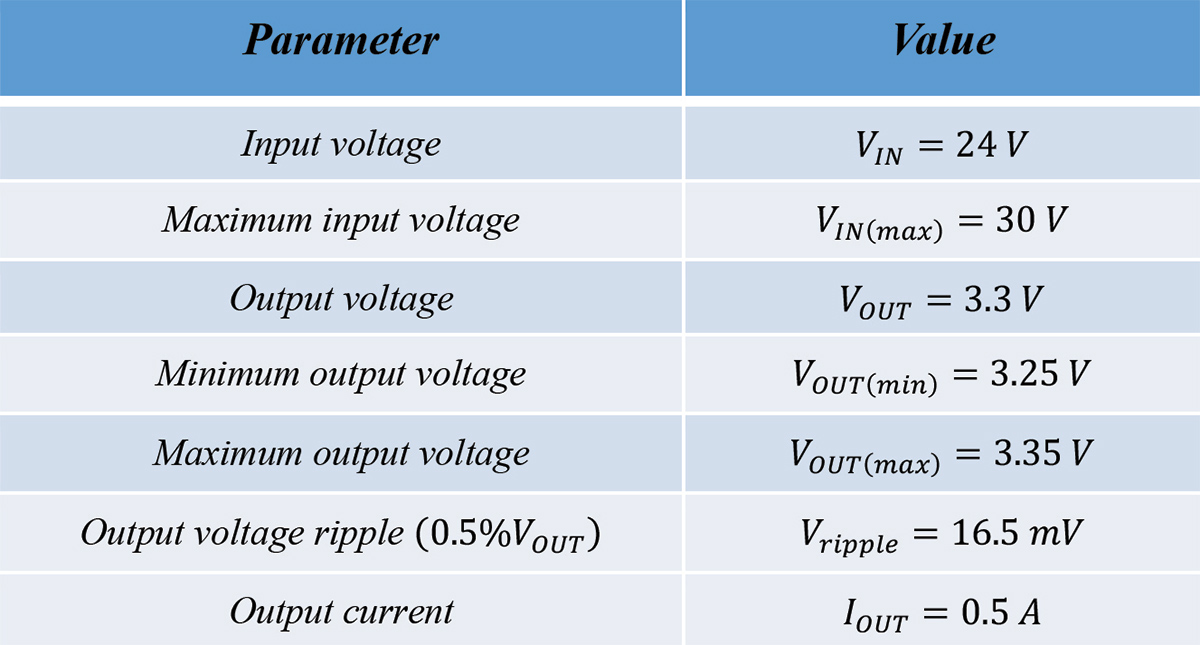

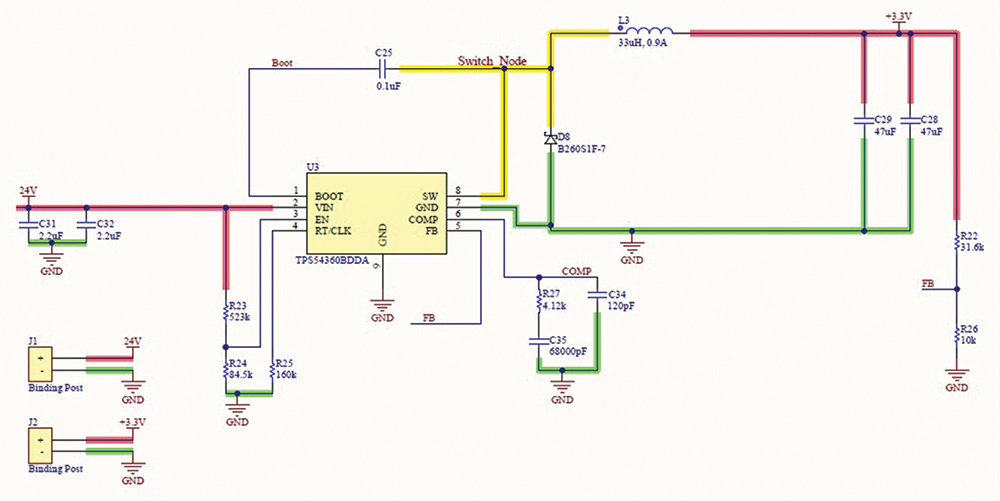

In this article, we present the schematic for the overall system, followed by a detailed schematic of a DC/DC SMPS. The design of a 24V-to-3.3 V DC/DC converter follows the design process philosophy where we start with a baseline functional schematic based on the IC manufacturer specifications. These specifications usually do not fully address non-functional concerns like thermal or EMC issues. We, therefore, address these issues and recommend design improvements to prevent failures during testing.

We conclude with a brief description of the next article.

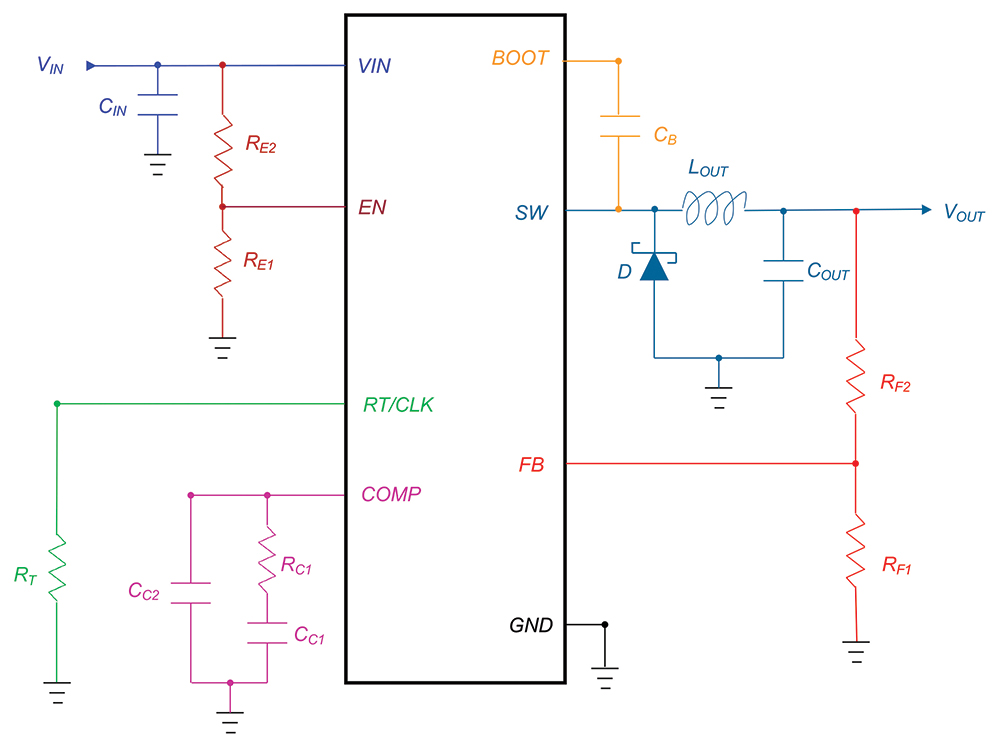

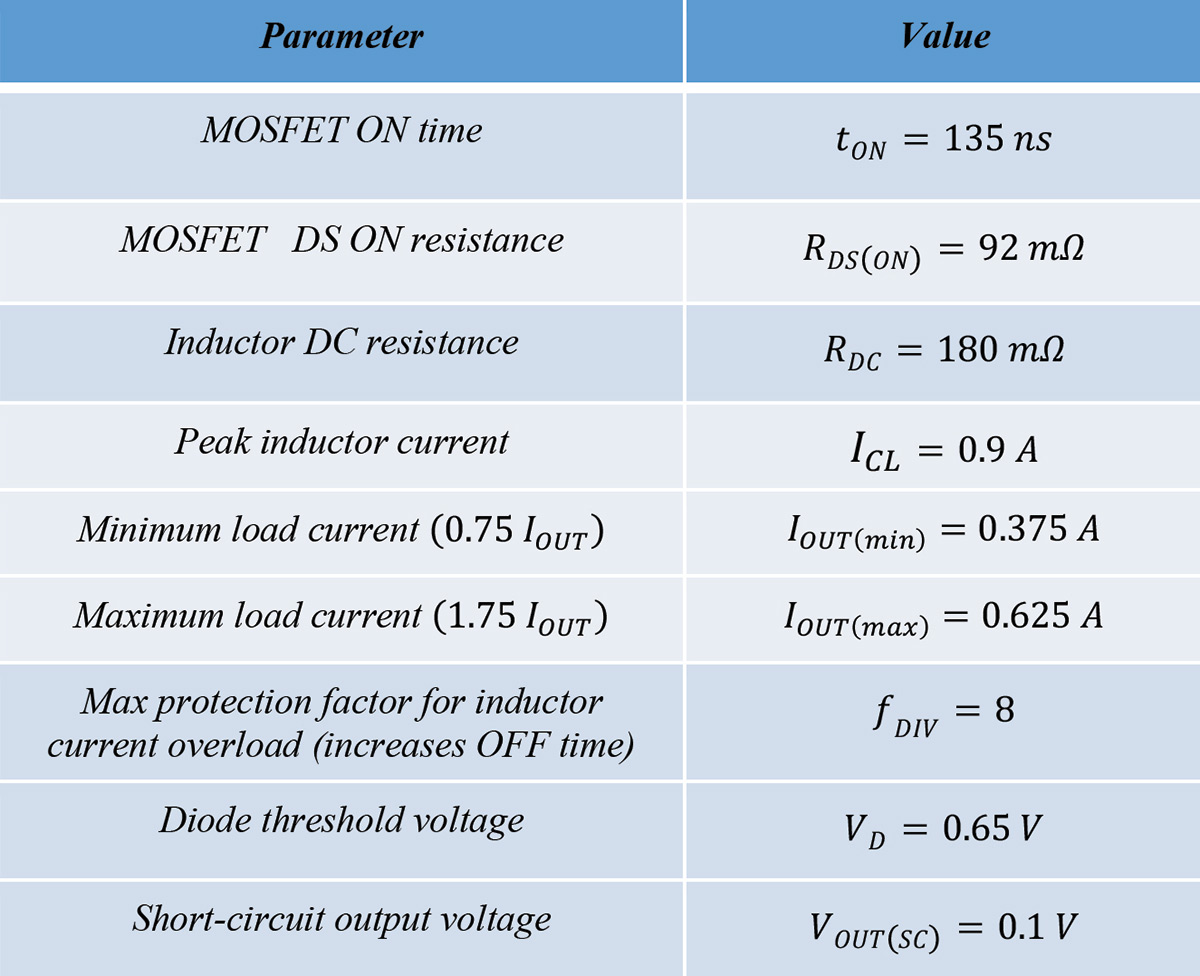

In our design, we use Texas Instruments TPS54360B step-down regulator with integrated high side n-channel MOSFET, [2]. The device implements constant frequency, current-mode control.

Additional assumptions and design constraints are listed in Table 2.

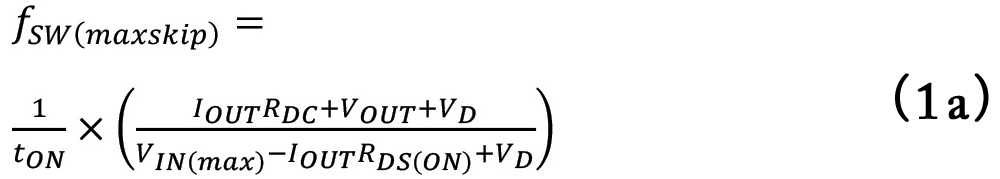

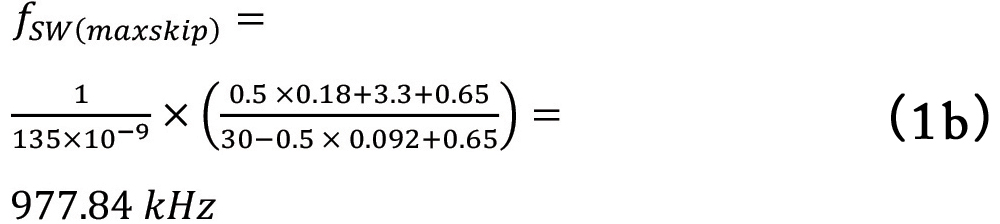

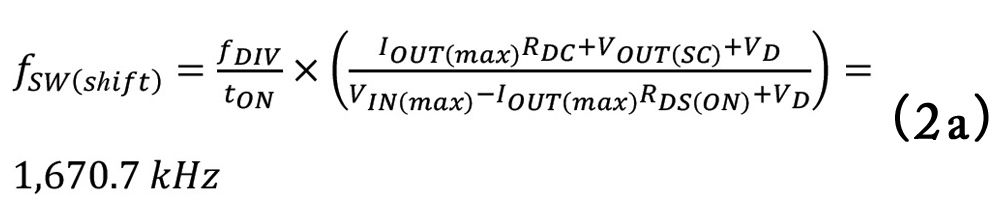

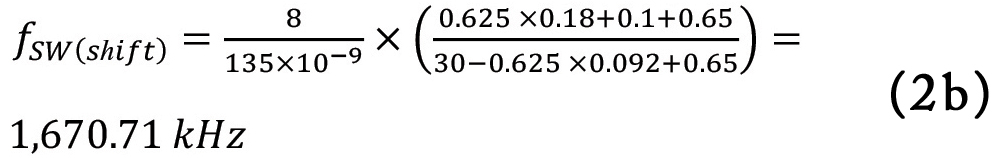

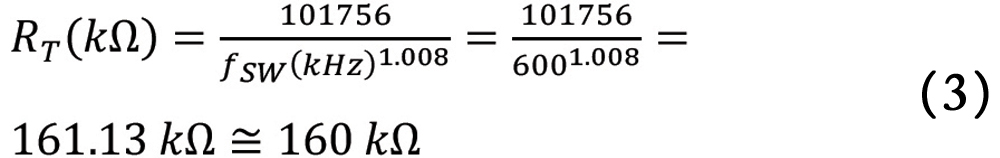

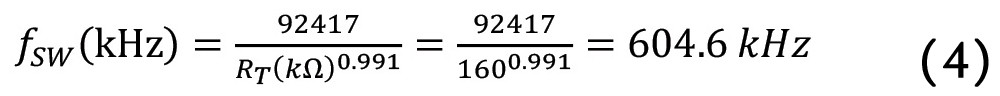

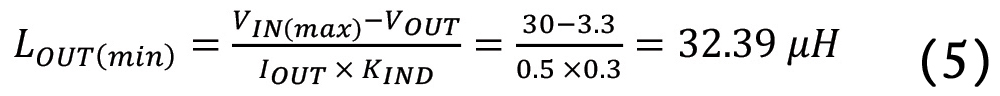

The switching frequency is adjusted using a (timing) resistor to ground connected to the RT/CLK pin. The timing resistance for a given switching frequency is determined from:

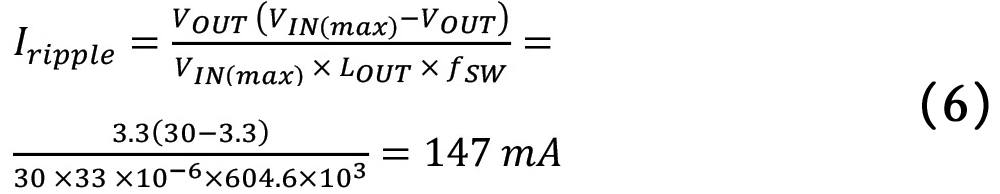

The inductor ripple current is calculated from

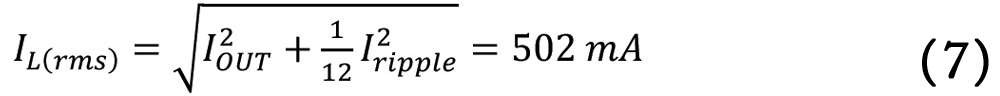

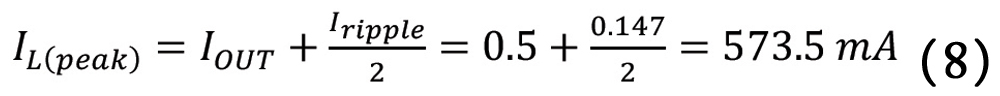

The inductor RMS current is calculated from

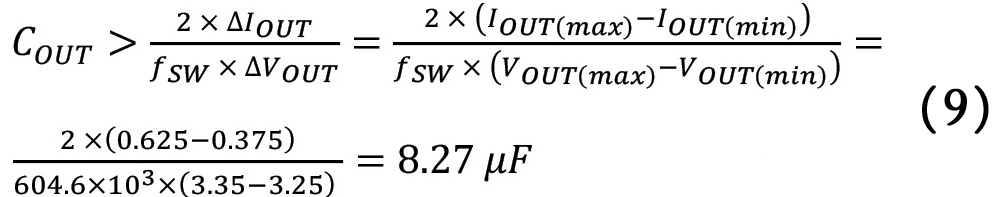

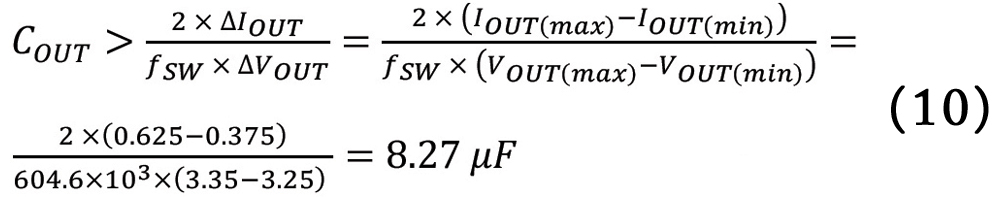

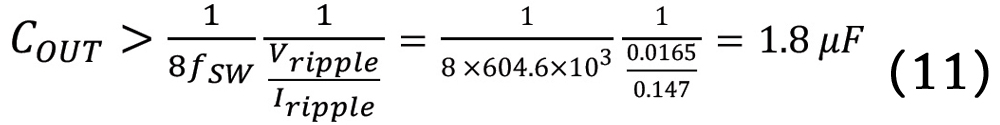

To account for the safety margin in our design, we chose two output capacitors in parallel, each of the value COUT = 47 μF.

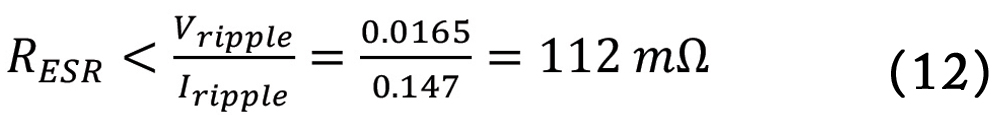

Maximum ESR of the output capacitor is calculated from

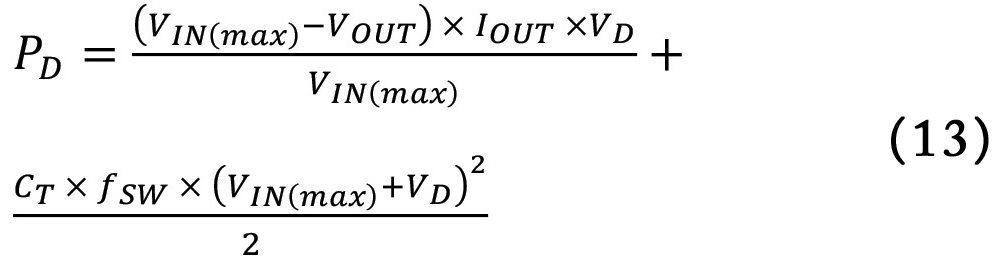

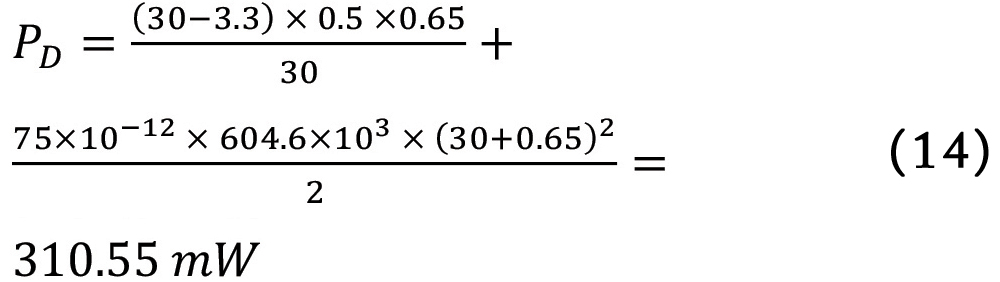

Thus, the power dissipation of the diode is

In our design, we use two Murata GCJ32DR72A225KA01L, 2.2 µF, 100V, ceramic capacitors in parallel.

In our design we use 0.1 µF, 50 V Murata GCJ188R71H104KA12D capacitor.

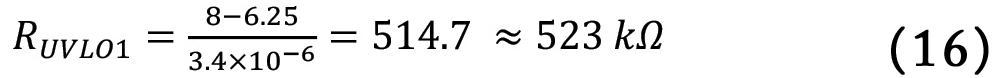

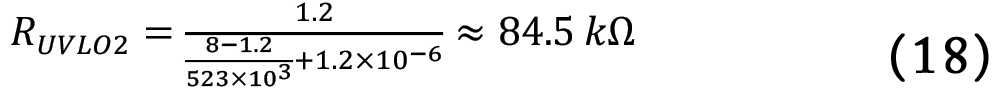

When adjusted to a non-default value of 4.3 V, the undervoltage lockout (UVLO) has two thresholds, one for power up when the input voltage is rising (UVLO start), and one for power down when the input voltage is falling (UVLO stop).

In our application, we chose UVLO start or VSTART = 8 V and UVLO stop or VSTOP = 6.25 V. Then the values of the two resistors are calculated as follows. The value of the resistor between E V and VIN, RUVLO1, is obtained from

If a low-side resistor, RLS = 10 kΩ is used, then the high side resistor value, RHS, is obtained from

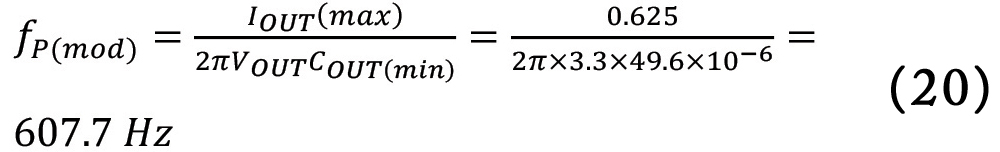

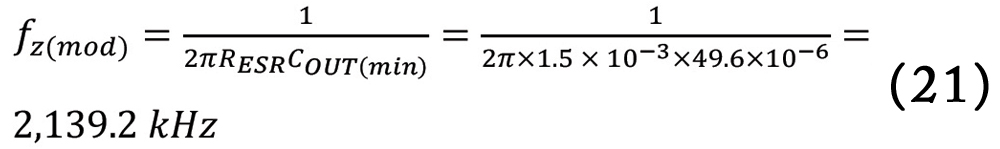

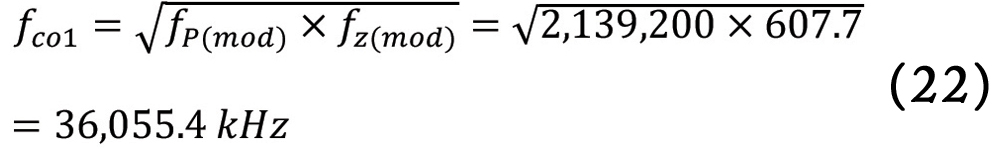

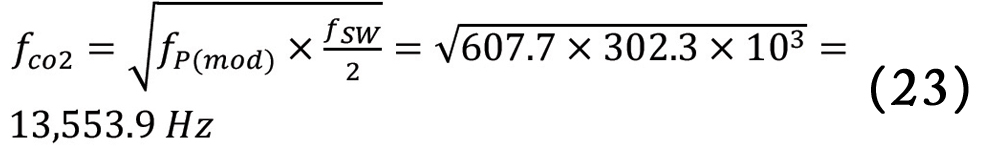

To design the compensation network, we follow the procedure outline in the regulator specifications. First, several frequencies are calculated.

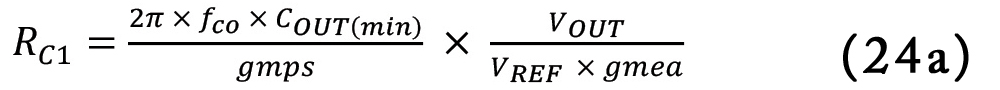

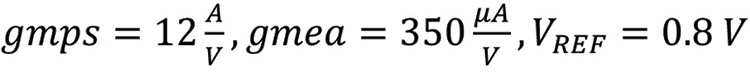

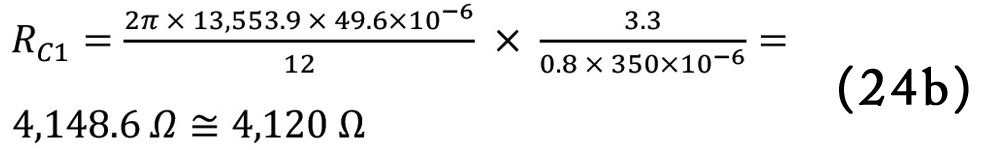

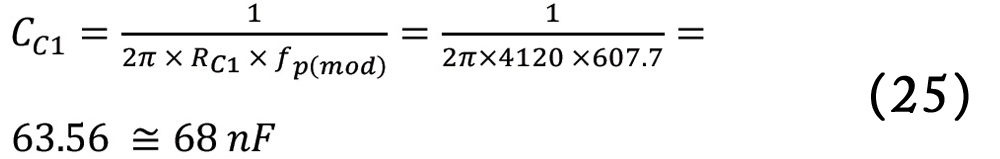

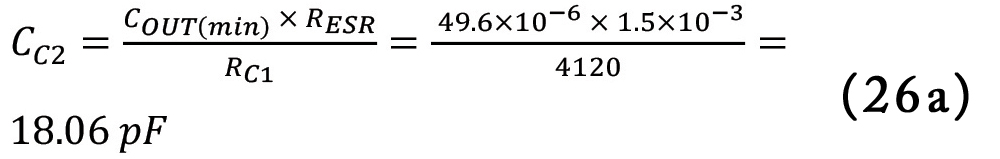

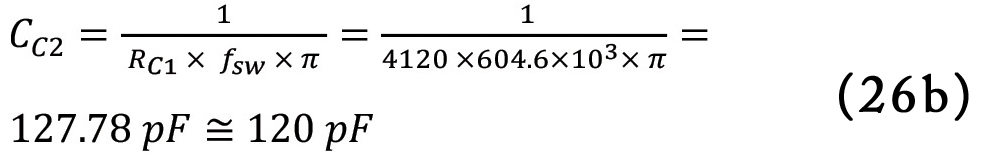

The resistor RC1 in the compensation network is calculated from

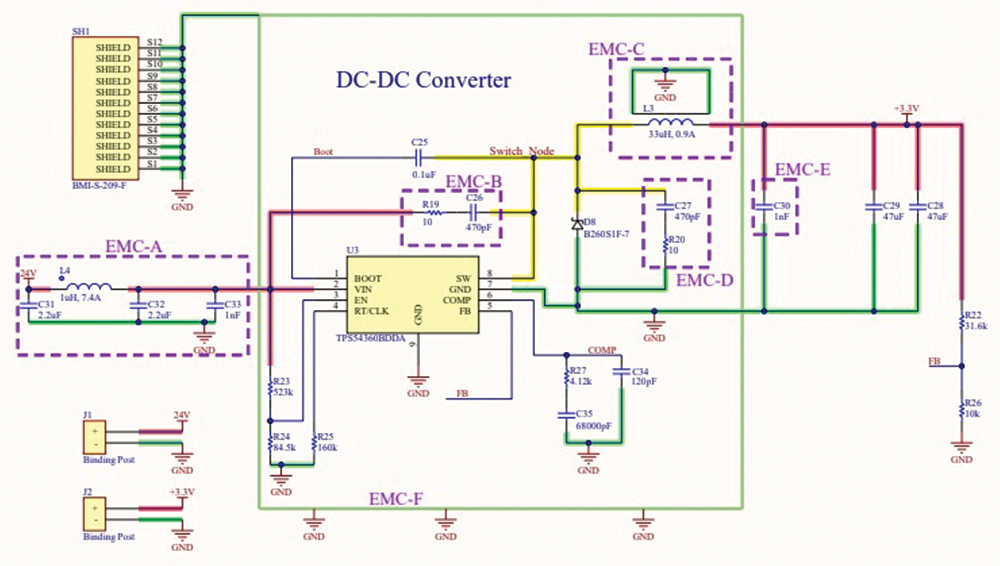

EMC-A: A 1nF capacitor (C33) is added on the Vin pin (U1.2) for high-frequency decoupling to reduce the amount of high-frequency energy generated by the DC-DC Converter that can conduct into the 24 V bus. Additionally, a π filter, [3], is constructed by adding a 1 µH inductor (L4) between the two input capacitors (C31 and C32).

EMC-B: A snubber circuit (series Resistor R19 & Capacitor C26) is added from SW Node (U1.8) to Vin (U1.2) because the Internal MOSFET is placed between these pins. This snubber is used to control the ringing from the internal MOSFET that results from the step response to the RLC network.

EMC-C: The Würth Elektronik inductor (L3) may be replaced with a Vishay IHLP inductor which is magnetically shielded or an IHLE inductor which is E-Field shielded to reduce radiated and conducted emissions further.

EMC-D: A snubber circuit (series Resistor R20 & Capacitor C27) is added across the catch diode to reduce ringing across the diode junction [4].

EMC-E: A 1nF capacitor (C30) is added near the inductor (L3) on the 3.3 V bus to filter high-frequency noise from conducting out onto the 3.3 V bus.

EMC-F: A shield (SH1) may be added if the PCB layout and EMC components are not successful to reducing the emissions from the DC-DC Converter. This may be needed in some instances where the EMC requirements are very stringent or the supply may be closely co-located to sensitive receivers.

These EMC components are designed into the first prototype as optional components that will be evaluated during emissions testing. The EMC performance may have trade-off decisions to make with regard to other requirements such as thermal, reliability, manufacturability, and cost. An example would be selecting the snubber values to optimize the EMC and thermal performance. Not all of the EMC components will likely be needed, and efforts will be made to remove the unneeded components to optimize cost.

- Adamczyk, B., Mee, S., Koeller, N, “Evaluation of EMC Emissions and Ground Techniques on 1- and 2-layer PCBs with Power Converters – Part 1:Top-Level Description of the Design Problem,” In Compliance Magazine, May 2021.

- https://www.ti.com/product/TPS54360B

- Adamczyk, B., Gilbert, B., “MC Filters Comparison Part II: π and T Filters,” In Compliance Magazine, January 2020.

- Mee, S., Teune, J., “Reducing Emissions In The Buck Converter SMPS,” IEEE EMC Symposium Record, 2002.