he trend toward society’s “smart‑electrification” is driving the need for ESD immunity at the system-level. IEC 61000‑4‑2 [1] defines how to perform the electrostatic discharge immunity test at the system level. Until about 15 years ago, protecting against such events involved implementing ad-hoc ESD protections (TVS – transient voltage suppressors) at board/system-level in proximity to the connectors interfacing with the “external world.”

However, a new trend of implementing system-level robustness at the component level (i.e., on-chip) is quickly becoming standard practice, mainly stemming from the desire to reduce system/board design costs.

While this may sound like a logical step on paper, it poses enormous challenges to the component ESD designer in that:

- IEC 61000-4-2 is not applicable at the component level, so every company is struggling to understand/design proprietary characterization methods at the component level to extrapolate performance at system-level; and

- ESD designers are now responsible for the performance of systems that they neither build nor, in many cases, know anything about.

This article is divided into two parts. This first part addresses the ESD design challenges stemming from ISO 10605 specs, while the second part will review the trade-offs between ESD design and EMC immunity requirements.

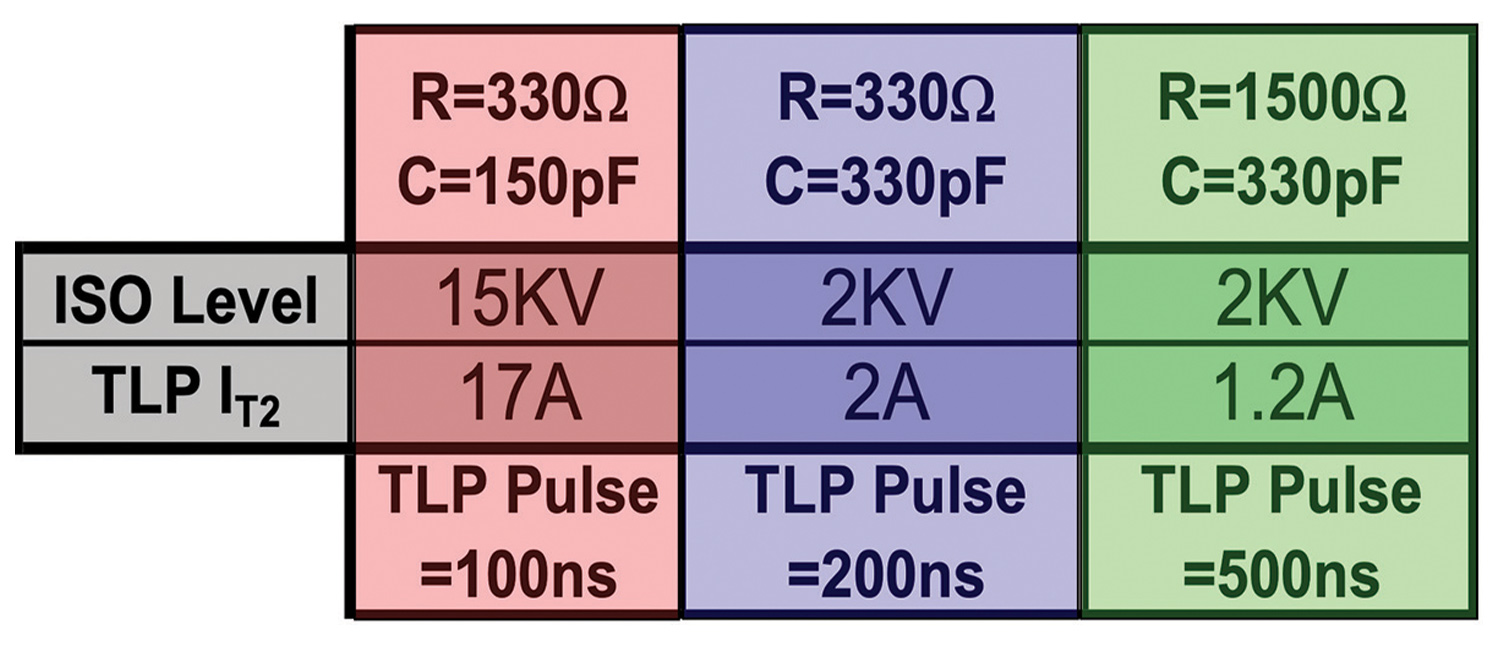

ISO 10605 specifies four different RC combinations (R=330Ω, R=1.5KΩ, C=150pF, and 330pF), leading to pulse decay times ranging from 60ns to 600ns. The actual RC combination(s) required at the board/system level may not be known at the time of component design. The straightforward consequence is that the ESD designer needs to validate the ESD solution on all four stress waveforms, with completely different pulse widths, energy contents, and rise times.

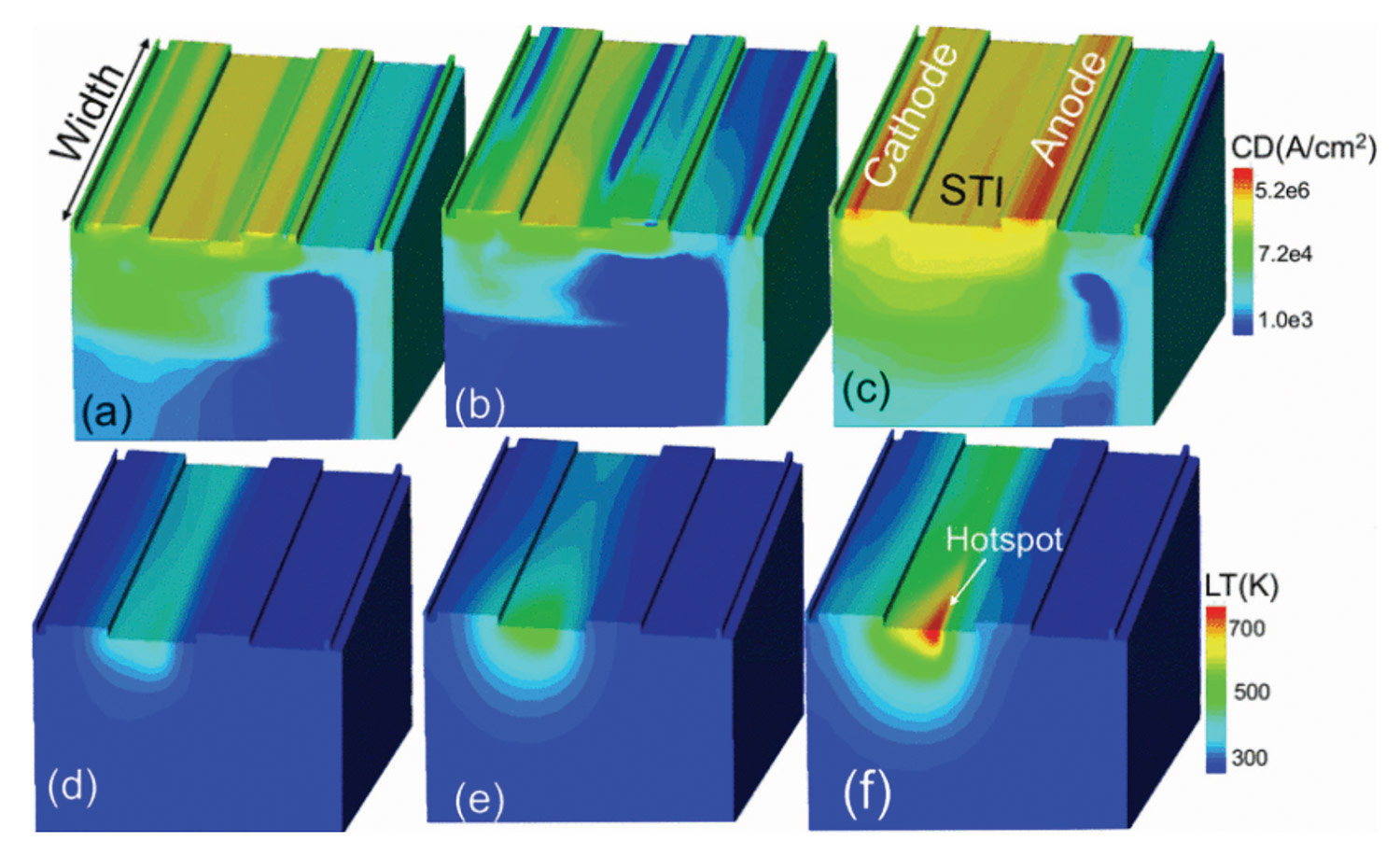

In [7], it was reported that an HV SCR meeting IEC Level 4 requirements (corresponding to ISO with R = 330Ω, and C = 150pF) miserably failed all other ISO stress permutations with larger capacitance and resistors. The root cause was identified in the lack of power scalability of the HV SCR caused by a static filament formation for pulses in excess of 100ns. A first-order correlation between TLP stress duration and ISO level was also established (see Figure 1 on page 22, [7]).

Unfortunately, the behavior of ESD clamps components used for system-level robustness is a strong function of the stress waveform. The bottom line is that it is virtually impossible to guarantee ESD system-level robustness at a component level without knowing all the details of the system/board implementation. A consequence of this fact is that the practice of specifying system‑level ESD robustness on a component’s datasheet is useless and could be misleading.

A typical parameter impacted by system implementation is rise time seen at the component level. It was reported in [9] that large inductive loads on CAN pins could increase the rise time of an ISO 10650 stress to >50ns. These slow values impacted the triggering mechanism of the ESD cell, causing non-uniform triggering, hence failing to meet the specifications. Again, a novel layout with internal back‑ballasting was devised to minimize the reliance of the ESD cell on rise time.

The automotive environment is extremely harsh for electronic systems. To guarantee reliable operation in all possible conditions, strict EMC immunity requirements are enforced. From an ESD perspective, EMC immunity requirements sometimes conflict with ESD requirements, making ESD-IP co-design extremely challenging.

However, component-level ESD cells designed to meet system-level ESD immunity can withstand a much higher energy level. Hence, it is becoming standard practice to have component-level ESD cells perform dual duty, i.e., to guarantee both ESD and EMC immunity to electrical disturbances. Hence, more and more component datasheets report robustness against ISO 7637 of pins that will connect to the external world.

The co-design of ESD immunity and immunity to electrical disturbances is not trivial. Besides the ability to withstand DC-like durations with test pulses 1, 2, and 5, slow rise times associated with them will require the ESD protection to be level‑triggered.

This implies the availability of a junction with appropriate breakdowns to support both ESD and EMC requirements.

In addition to immunity to electrical disturbances, automotive systems must be robust in their defense against RF disturbances as well per IEC62132-4. A direct power injection (DPI) method is used to measure the electromagnetic immunity of an IC from 150KHz to 1GHz. The interaction between ESD immunity and DPI is not straightforward, as both ESD and DPI have fast-rising voltage edges, although with different amplitudes.

In [11], the case of a LIN pin passing ESD immunity but failing the DPI test was reported. It was found that the noise injected into the substrate (and then coupled to the LIN pin) by the RC-triggered ESD cell during the DPI test was the culprit for the test failure. A new, level-triggered ESD cell had to be devised to address the issue. In a similar fashion, in [12], a robust RC-triggered ESD cell failed DPI testing, mainly at low frequencies. A redesign of the RC-triggering circuit was needed to address the issue, as it was not possible to design an effective level-trigger ESD cell for ESD immunity.

From the above examples, it would seem that level-triggered ESD cells are necessary to meet DPI requirements. However, there are situations where RC-triggered ESD cells are highly desirable. One such scenario is when inductive fly-back protection is needed. This is typically the case for output pins driving inductive loads, such as external cables and/or chokes. When the power supply is switched off, it is convenient (i.e., no additional inductive flyback protection is needed) to release the energy stored in the inductors through the ESD cell. This is typically done through RC-triggering the ESD cell in MOS conduction mode to keep voltages at safe levels. As seen from the above example, functional requirements can lead to opposite design requirements on ESD cells.

Conclusion

- ISO 10605 “Road vehicles – Test methods for electrical disturbances from ESD.”

- IEC 61000- 4-2: “Electromagnetic compatibility (EMC), Part 4-2: Testing and measurement techniques – Electrostatic discharge immunity test.”

- ISO 7637-1:2002 (E) “Road vehicles – Electrical disturbances from conduction and coupling – Part 1: Definitions and general considerations,” Second edition 2002-03-15, https://www.iso.ch.

- ISO 7637-2:2004 (E) “Road vehicles -Electrical disturbances from conduction and coupling – Part 2: Electrical transient conduction along supply lines only,” Second edition 2004-06-15, https://www.iso.ch.

- ISO 7637-3:1995 (E) “Road vehicles – Electrical disturbance by conduction and coupling – Part 3: Vehicles with nominal 12 V, 24 V or 42 V supply voltage – Electrical transient transmission by capacitive and inductive coupling via lines other than supply lines,” 2007.

- IEC 62132-4, 2007, “Electromagnetic Compatibility (EMC), Integrated Circuits, Measurement of Electromagnetic Immunity 150 kHz to 1 GHz – Part 4: Direct RF Power Injection Method.”

- G. Boselli, A. Salman, J. Brodsky, and H. Kunz, “The relevance of long-duration TLP stress on system level ESD design,” Proceedings of 2010 EOS/ESD Symposium.

- P. Besse, J.-P. Laine, A. Salles, and M. Baird, “Correlation between System Level and TLP Tests Applied to Stand-alone ESD Protections and Commercial Products,” Proceedings of 2010 EOS/ESD Symposium.

- A. Salman, F. Farbiz, A. Concannon, H. Edwards, and G. Boselli, “Mutual Ballasting: A Novel Technique for improved Inductive System Level IEC ESD stress performance for Automotive Applications”, Proceedings of 2013 EOS/ESD Symposium.

- K. Nagothu, J. Di Sarro, R. Sankaralingam, G. Boselli, and M. Shrivastava, “Insights into the System-Level IEC ESD Failure in High Voltage DenMOS-SCR for Automotive Applications,” Proceedings of 2020 EOS/ESD Symposium.

- B. Deutschmann, F. Magrini, and Y. Cao, “Robustness of ESD Protection Structures against Automotive Transient Disturbances,” Proceedings of 2010 Asia-Pacific International Symposium on Electromagnetic Compatibility.

- K. Abouda, P. Besse, and E. Rolland, “Impact of ESD Strategy on EMC performances,” in Proceedings of 2011 Workshop on Electromagnetic Compatibility of Integrated Circuits.

- Y. Xiu, F. Farbiz, A. Salman, Y. Zu, M. Dissegna, G. Boselli, and E. Rosenbaum, “Case Study of DPI Robustness of a MOS-SCR Structure for Automotive Applications,” Proceedings of 2016 EOS/ESD Symposium.