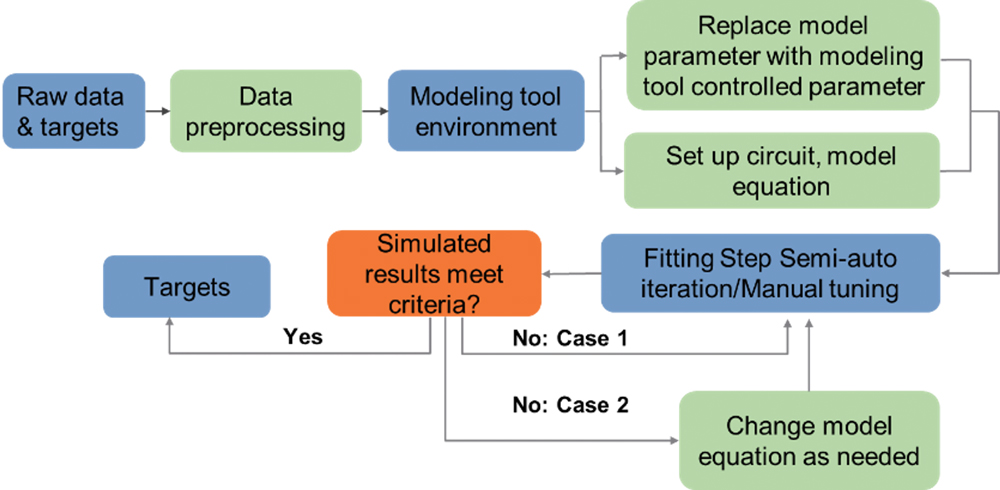

In conventional compact model fitting, the modeler fits the model by tuning the parameters of the physical device equations. Figure 2 shows the flow chart of conventional ESD compact modeling fitting. As we mentioned, the fitting step is very time-consuming, and sometimes, the modeler must change the model equations to get the simulated I-V fitted to hardware data and pass the quality check criteria.

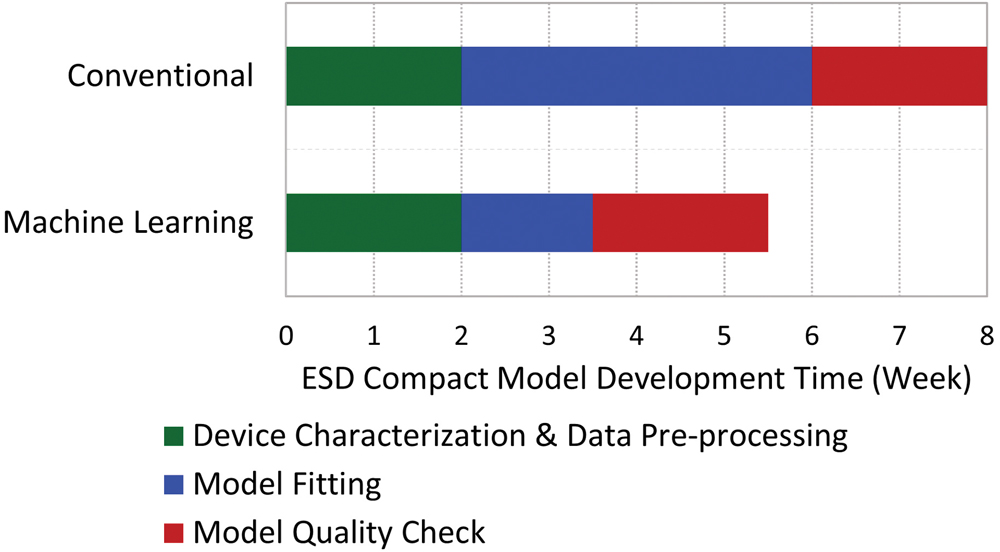

For efficiency, model development can usually be categorized into three phases: device characterization and data-pre-processing, model fitting, and model quality check. Figure 4 shows the development time comparison between the conventional and novel ESD compact model development. Using the conventional methodology, an 8-week timeline is typically quoted by an experienced ESD device modeler on a new ESD diode model with TLP, vf-TLP, and DC characteristics. As a comparison, to develop the same model using a novel ESD compact modeling methodology, the model fitting step could save up to 62% of the time, which brings the overall development time saving to 31%. More time could be saved if Machine Learning techniques are applied to data processing and quality checks in the future.

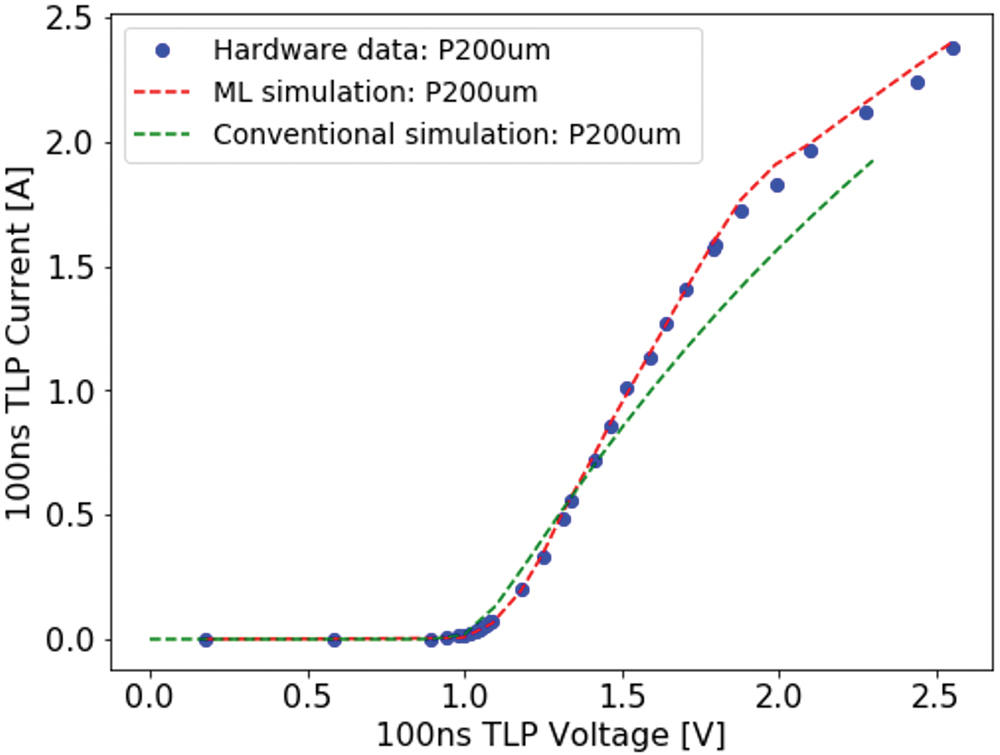

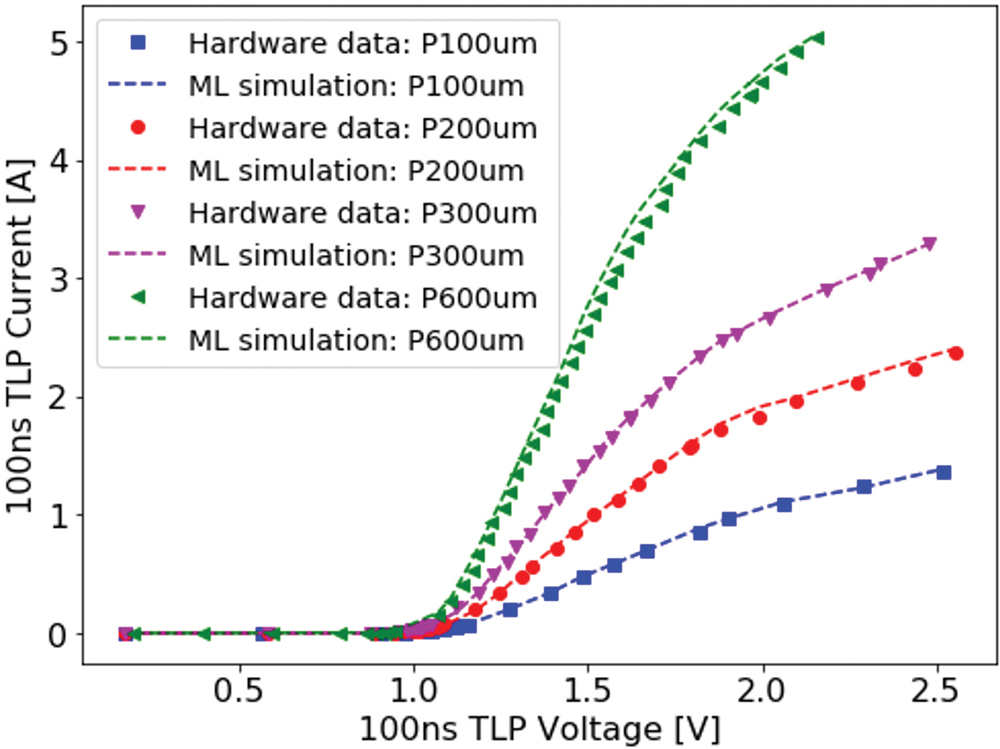

Overall, the novel machine learning-based ESD model will significantly simplify the development work and improve the model prediction accuracy over the traditional SPICE model. It could also achieve some challenging work that traditional SPICE models are not good at, like fitting for I-V characteristics with snapback behavior. It would bring evolutionary changes to future ESD compact modeling work.

- W. Liang, X. Yang, M. Miao, A. Loiseau, S. Mitra and R. Gauthier, “Novel ESD Compact Modeling Methodology Using Machine Learning Techniques for Snapback and Non-Snapback ESD Devices,” in IEEE Transactions on Device and Materials Reliability, vol. 21, no. 4, pp. 455‑464, December 2021, doi: 10.1109/TDMR.2021.3116599.