Part 1

Integrated circuits intended for automotive applications have higher electrostatic discharge (ESD) qualification requirements than those intended for commercial and consumer electronics. This article is in two parts. Part 1 will discuss why electronic components intended for automotive applications might require more stringent requirements and then review the high-level differences between conventional ESD qualification and automotive qualifications. Part 2, to be in next month’s issue of In Compliance, will give the specific additional requirements for human body model (HBM) and charged device model (CDM) for automotive qualification.

(This article had its origin in a series of blog posts on ESD testing available at http://www.srftechnologies.com/ESD-RESOURCES.html.)

Automobiles have always had electrical circuits. Even before electric headlights and electric starters, magnetos provided electrical pulses to power spark plugs. The amount of electrical circuitry increased steadily over the years, and today, the radio was replaced long ago as the most sophisticated piece of electronics in a vehicle. The rapid expansion in the high-tech electronic content in automobiles has attracted increased interest across a much wider section of the electronics industry than in the past. Integrated circuit suppliers wishing to become suppliers to the automotive industry must become familiar with the qualification requirements for automotive electronics.

The working environment for automotive electronics is much more severe than is common for most consumer applications. Automotive electronics must work in the dead of winter in Minnesota and crossing Death Valley in the summer. The automotive environment is also an electrically noisy environment, with wiring harnesses carrying sensing circuits as well as high current pulses to operate a wide range of motors and accessories. Automotive electronics are often safety critical. It is, therefore, not surprising that the automotive industry has its own set of qualification requirements for electronic components.

Note: This article will summarize the differences between ESD qualification for commercial and automotive integrated circuits. However, this summary should not be a substitute for a thorough reading of the full standards.

- A list of stress tests required for qualification such as:

- ⚬ High Temperature Operation Life

- ⚬ Early Life Failure Rate

- ⚬ Temperature Humidity Bias

- ⚬ Human Body Model (HBM)

- ⚬ Charged Device Model (CDM)

- Specification of the test method to be used for each test

- ⚬ JEDEC: mostly JEDEC tests, but some Military

- ⚬ AEC: a combination of AEC-specific tests, as well as JEDEC and Military tests

- Specification of requirements for each test such as:

- ⚬ Temperature for test

- ⚬ Humidity during test

- ⚬ Sample size

- ⚬ Number of failed samples allowed

- ⚬ Failure criteria

- When each of the tests is required such as:

- ⚬ Design change

- ⚬ Change of gate oxide

- ⚬ Change of metallization

- ⚬ New fabrication site

- A list of stress tests required for qualification such as:

- ⚬ High Temperature Operation Life

- ⚬ Early Life Failure Rate

- ⚬ Temperature Humidity Bias

- ⚬ Human Body Model (HBM)

- ⚬ Charged Device Model (CDM)

- Specification of the test method to be used for each test

- ⚬ JEDEC: mostly JEDEC tests, but some Military

- ⚬ AEC: a combination of AEC-specific tests, as well as JEDEC and Military tests

- Specification of requirements for each test such as:

- ⚬ Temperature for test

- ⚬ Humidity during test

- ⚬ Sample size

- ⚬ Number of failed samples allowed

- ⚬ Failure criteria

- When each of the tests is required such as:

- ⚬ Design change

- ⚬ Change of gate oxide

- ⚬ Change of metallization

- ⚬ New fabrication site

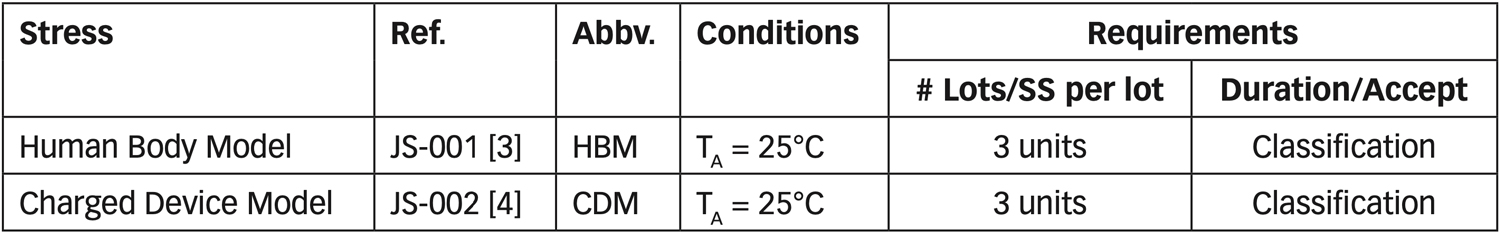

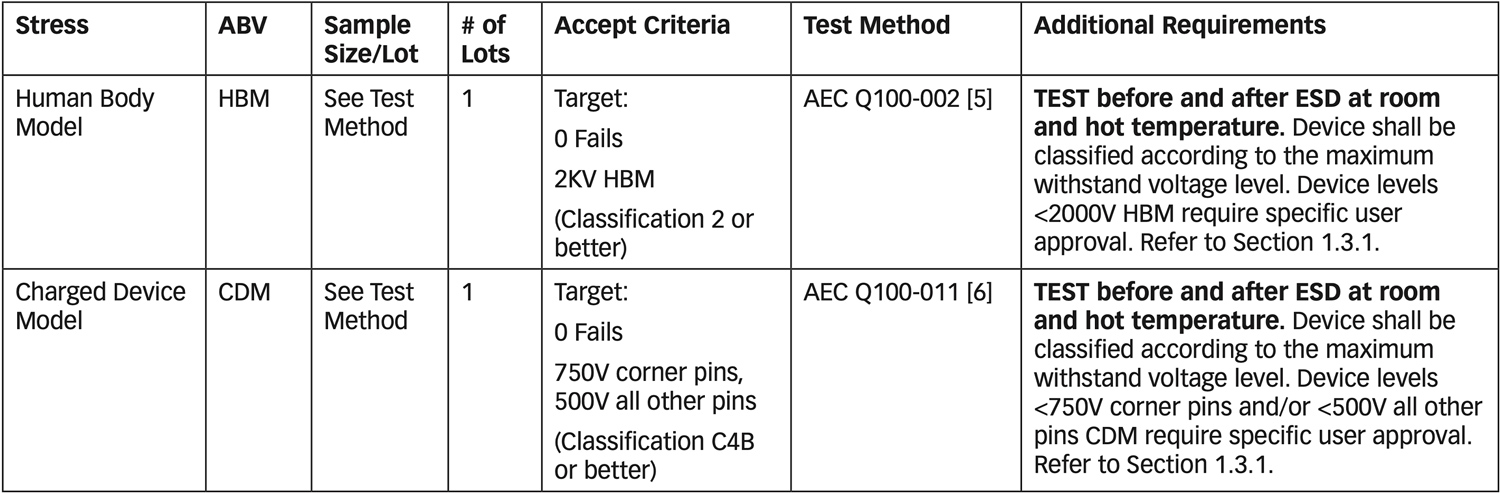

There are three notable differences between the qualification requirements in the two methods:

- The test standards differ between JEDEC and AEC for both HBM and CDM

- The requirements differ

- ⚬ JEDEC requires “Classification.”

- ⚬ AEC gives specific target levels for both HBM and CDM.

- JEDEC requires three samples, while AEC says, “See Test Method.”

- The test standards differ between JEDEC and AEC for both HBM and CDM

- The requirements differ

- ⚬ JEDEC requires “Classification.”

- ⚬ AEC gives specific target levels for both HBM and CDM.

- JEDEC requires three samples, while AEC says, “See Test Method.”

All HBM testing performed on Integrated Circuit Devices to be AEC Q100 qualified shall be compliant to the latest revision of the ANSI/ESDA/JEDEC JS-001 specification, with additional requirements as defined herein.

All CDM ESD testing performed on Integrated Circuit devices to be AEC Q100 qualified shall be per the latest version of the ANSI/ESDA/JEDEC JS‑002 specification with the following clarifications and requirements.

These statements show that the basic test methods for HBM and CDM, JS-001 and JS-002, are the same for JEDEC and AEC. JS-001 and JS-002 are joint standards developed by joint JEDEC and the Electrostatic Discharge Association (ESDA) working groups.

The difference in requirements is more substantial. JEDEC lists the requirements as “Classification.” The requirement is, therefore, that all integrated circuit designs must be tested for both HBM and CDM. The actual requirement is set by agreement between the manufacturer of the integrated circuit and the purchaser. For many years it was “common knowledge” that the specification for HBM was 2000 V and that that requirement was being reduced to 1000 V due to the activity of the Industry Council on ESD Targets. This “common knowledge” was, in fact, never true; for commercial product, the ESD levels for both HBM and CDM have always been an agreement between supplier and purchaser.

AEC is much stricter in terms of requirements for HBM and CDM. The basic benchmarks for AEC ESD are an HBM passing level of 2000 V and a CMD passing level of 750 V for corner pins and 500 V for all other pins. As can be seen in Table 2, there are exceptions. Lower levels of ESD robustness can be accepted by the user. The note to see Section 1.3.1 is a requirement for reporting, which reads:

For ESD, it is highly recommended that the passing voltage be specified in the supplier datasheet with a footnote on any pin exceptions. This will allow suppliers to state, e.g., “AEC-Q100 qualified to ESD Classification 2.”

Most of the remaining differences between the JEDEC and AEC ESD requirements are in the additional requirement in Q100-002 for HBM and Q100-011 for CDM.

Summary

- JESD47, “Stress-Test-Driven Qualification of Integrated Circuits,” JEDEC Solid State Technology Association, https://www.jedec.org.

- AEC – Q100 – Rev-H, “Failure Mechanism Based Stress Test Qualification for Integrated Circuits,” Automotive Electronics Council, http://www.aecouncil.com.

- ANSI/ESDA/JEDEC JS-001-2017, “For Electrostatic Discharge Sensitivity Testing, Human Body Model (HBM) – Component Level,” EOS/ESD Association, https://www.esda.org, and JEDEC Solid State Technology Association, https://www.jedec.org.

- ANSI/ESDA/JEDEC JS-002-2018, “For Electrostatic Discharge Sensitivity Testing, Charged Device Model (CDM) – Device Level,” EOS/ESD Association, https://www.esda.org, and JEDEC Solid State Technology Association, https://www.jedec.org.

- AEC–Q100-002 REV-E, “Human Body Model Electrostatic Discharge Test,” Automotive Electronics Council, http://www.aecouncil.com.

- AEC-Q100-011 Rev-D, “Charged Device Model (CDM) Electrostatic Discharge (ESD) Test,” Automotive Electronics Council, http://www.aecouncil.com.